## **LAPORAN PRAKTIKUM**

**Mata Kuliah**

**Pengantar Sistem Digital**

### **RANGKAIAN ADDER DAN COMPARATOR**

**Dosen: Arif R. Dwiyanto ST., MTI.**

**Disusun oleh:**

**Siti Indri Rahma (202410715022)**

**F3A6**

**PROGRAM STUDI INFORMATIKA FAKULTAS ILMU KOMPUTER**

**UNIVERSITAS BHAYANGKARA JAKARTA RAYA**

**2025**

# BAB I

## PENDAHULUAN

### 1.1 Tujuan Praktikum

1. Mahasiswa memahami konsep rangkaian kombinasi.

2. Mahasiswa mampu membangun rangkaian 8-bit Adder menggunakan Logisim.

3. Mahasiswa mampu membangun rangkaian Comparator menggunakan logisim.

4. Menguji kebenaran fungsi dengan membandingkan hasil penjumlahan input terhadap output yang dihasilkan.

### 1.2 Langkah-langkah Kerja

1. Membuat 8-bit Adder

- Tabel kebenaran

| Ai | Bi | Cin | Sum | Cout |

|----|----|-----|-----|------|

| 0  | 0  | 0   | 0   | 0    |

| 0  | 0  | 1   | 1   | 0    |

| 0  | 1  | 0   | 1   | 0    |

| 0  | 1  | 1   | 0   | 1    |

| 1  | 0  | 0   | 1   | 0    |

| 1  | 0  | 1   | 0   | 1    |

| 1  | 1  | 0   | 0   | 1    |

| 1  | 1  | 1   | 1   | 1    |

Tabel kebenaran 8-bit adder direpresentasikan melalui tabel kebenaran full adder, karena 8-bit adder disusun dari delapan buah full adder yang beroperasi secara berantai. Rangkaian Adder ini memiliki total 16 bit, sehingga menghasilkan kombinasi masukan sebesar  $2^{16}$  atau 65.536 baris pada tabel kebenaran. Setiap full adder memiliki tiga input (A, B, dan C-in) serta dua output (Sum dan C-out).

- Bangun rangkaian 8-bit adder dengan ekspreksi logika berikut:

Rumus umum:

$$Si = Ai \oplus Bi \oplus Ci$$

$$Ci + 1 = (Ai \cdot Bi) + (Ci \cdot (Ai \oplus Bi))$$

Ekspresi logika 8-bit adder:

$$\begin{aligned}

S_0 &= A_0 \oplus B_0 \oplus C_0 \\

C_1 &= (A_0 \cdot B_0) + (C_0 \cdot (A_0 \oplus B_0)) \\

S_1 &= A_1 \oplus B_1 \oplus C_1 \\

C_2 &= (A_1 \cdot B_1) + (C_1 \cdot (A_1 \oplus B_1)) \\

S_2 &= A_2 \oplus B_2 \oplus C_2 \\

C_3 &= (A_2 \cdot B_2) + (C_2 \cdot (A_2 \oplus B_2)) \\

S_3 &= A_3 \oplus B_3 \oplus C_3 \\

C_4 &= (A_3 \cdot B_3) + (C_3 \cdot (A_3 \oplus B_3)) \\

S_4 &= A_4 \oplus B_4 \oplus C_4 \\

C_5 &= (A_4 \cdot B_4) + (C_4 \cdot (A_4 \oplus B_4)) \\

S_5 &= A_5 \oplus B_5 \oplus C_5 \\

C_6 &= (A_5 \cdot B_5) + (C_5 \cdot (A_5 \oplus B_5)) \\

S_6 &= A_6 \oplus B_6 \oplus C_6 \\

C_7 &= (A_6 \cdot B_6) + (C_6 \cdot (A_6 \oplus B_6)) \\

S_7 &= A_7 \oplus B_7 \oplus C_7 \\

C_8 &= (A_7 \cdot B_7) + (C_7 \cdot (A_7 \oplus B_7)) \rightarrow \text{Carry akhir (Cout)}

\end{aligned}$$

Ekspresi logika pada adder 8-bit menggunakan operasi XOR untuk menghasilkan keluaran Sum dan kombinasi AND-OR untuk menghasilkan Carry. Perhitungan dilakukan berantai dari bit paling rendah hingga bit paling tinggi, di mana hasil Carry sebuah bit menjadi Carry-in untuk bit berikutnya.

- Menyusun rangkaian menggunakan delapan gerbang XOR dan delapan gerbang AND pada Logisim.

- Hubungkan input A dan B menggunakan Constant.

- Tambahkan LED pada output Sum (S) dan Carry (C).

## 2. Comparator

- Tabel kebenaran

| A | B | Output A > B | Output A = B | Output A < B |

|---|---|--------------|--------------|--------------|

| 0 | 0 | 0            | 1            | 0            |

| 0 | 1 | 0            | 0            | 1            |

| 1 | 0 | 1            | 0            | 0            |

| 1 | 1 | 0            | 1            | 0            |

Tabel kebenaran 8-bit comparator tidak dapat dilakukan secara praktis karena kompleksitasnya sangat tinggi. Rangkaian comparator ini memiliki total 16 bit

masukan (8 bit untuk input A dan 8 bit untuk input B), sehingga menghasilkan kombinasi masukan sebesar  $2^{16}$  atau 65.536 baris pada tabel kebenaran. Dalam rangkaian 8-bit comparator terdapat tiga keluaran ( $A > B$ ,  $A = B$ ,  $A < B$ ) karena ketiga kondisi tersebut merupakan satu-satunya kemungkinan hasil yang dapat terjadi ketika dua bilangan biner dibandingkan. Apabila nilai biner A lebih besar daripada nilai biner B, maka keluaran  $A > B$  bernilai 1, sementara keluaran lainnya akan bernilai 0. Jika nilai A sama dengan B, maka keluaran  $A = B$  bernilai 1, sedangkan pada kondisi ketika nilai A lebih kecil dibanding nilai B, keluaran  $A < B$  bernilai 1.

- Menentukan kondisi perbandingan bit menggunakan tiga sinyal logika

- $(A = B): E_i = (A_i \oplus B_i)'$

- $(A > B): G_i = A_i \cdot B_i'$

- $(A < B): L_i = A_i' \cdot B_i$

- Menyusun ekspresi logika

- $A = B$ , akan bernilai benar jika semua bit bernilai sama

$$(A = B) = E_7 \cdot E_6 \cdot E_5 \cdot E_4 \cdot E_3 \cdot E_2 \cdot E_1 \cdot E_0$$

- $A > B$ , akan bernilai benar jika pada suatu bit ke- $i$ ,  $A > B$  dan semua bit yang lebih signifikan bernilai sama

$$A > B = G_7 + (E_7 G_6) + (E_7 E_6 G_5) + (E_7 E_6 E_5 G_4) + \dots + (E_7 E_6 E_5 E_4 E_3 E_2 E_1 G_0)$$

- $A < B$ , akan bernilai benar jika pada suatu bit ke- $i$ ,  $A < B$  dan semua bit yang lebih signifikan bernilai sama

$$A < B = L_7 + (E_7 L_6) + (E_7 E_6 L_5) + (E_7 E_6 E_5 L_4) + \dots + (E_7 E_6 E_5 E_4 E_3 E_2 E_1 L_0)$$

- Menggabungkan semua sinyal kesetaraan

Semua output kesetaraan ( $E_7-E_0$ ) dikombinasikan secara berantai menggunakan gerbang AND

- Menentukan prioritas perbandingan. Jika terdapat bit ke- $i$  (dimulai dari MSB) dengan  $G_i = 1$ , maka hasil akhir adalah  $A > B$ , dan rangkaian berhenti mengevaluasi bit yang lebih rendah. Jika terdapat bit ke- $i$  dengan  $L_i = 1$ , maka hasil akhir adalah  $A < B$ .

- Menggabungkan logika hasil ( $G$ ,  $L$ ,  $E$ )

- Sinyal  $A > B$  diperoleh dari kondisi  $G7 + (E7 \cdot G6) + (E7 \cdot E6 \cdot G5) + \dots + (E7 \cdot E6 \dots E1 \cdot G0)$

- Sinyal  $A < B$  diperoleh dari kondisi sebaliknya

- Sinyal  $A = B$  bernilai 1 jika seluruh  $Ei = 1$

- Meneruskan sinyal ke output akhir

- EQ (Equal /  $A == B$ )

- GT (Greater /  $A > B$ )

- LT (Less /  $A < B$ )

### 1.3 Hasil Simulasi

#### 1. 8-bit Adder

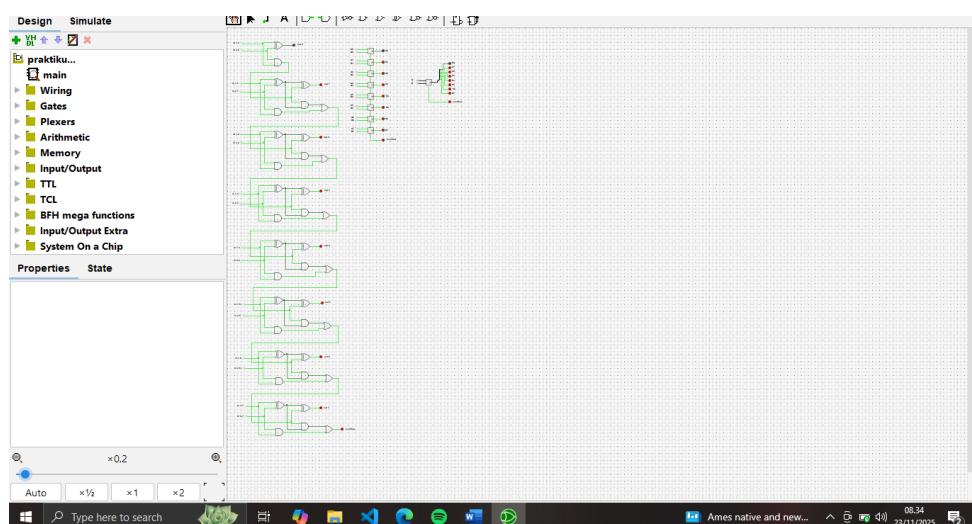

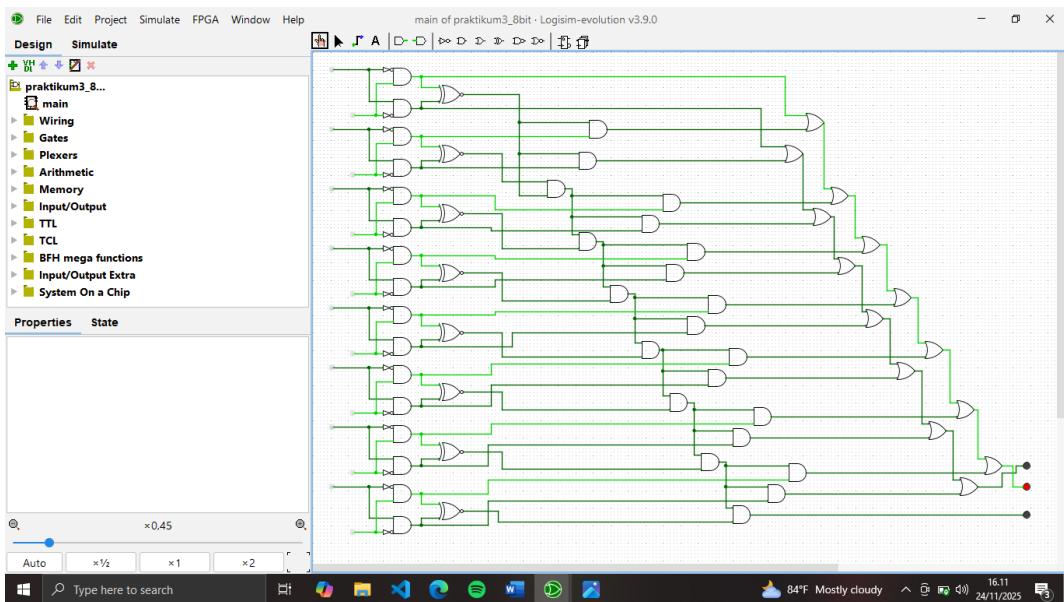

- Gerbang Logika

Rangkaian penjumlahan biner 8-bit diimplementasikan menggunakan gerbang logika dasar atau full-adder. Proses penjumlahan dimulai dari bit terendah ( $A_0, B_0$ ) di mana setiap bit melakukan operasi penjumlahan dan menghasilkan sum serta carry-out. Sinyal sum dihasilkan dari dua tingkat gerbang XOR. Satu untuk  $A \oplus B$ , dan hasil ini di-XOR-kan lagi dengan carry-in ( $C_{in}$ ) untuk mendapatkan Sum ( $A_0 \oplus B_0 \oplus C_{in}$ ). Sementara, carry-out ( $C_{out}$ ) dihasilkan dari kombinasi tiga gerbang AND yang di-OR-kan ( $C_{out} = (A_i \cdot B_i) + (C_{i-1} \cdot (A_i \oplus B_i))$ ). Carry-out di setiap full adder diteruskan sebagai carry-in ke full adder berikutnya, membentuk rangkaian ripple carry adder 8-bit. Hasil penjumlahan (sum) ditampilkan pada delapan LED, dan carry terakhir dari bit ke-7 berfungsi sebagai indikator overflow.

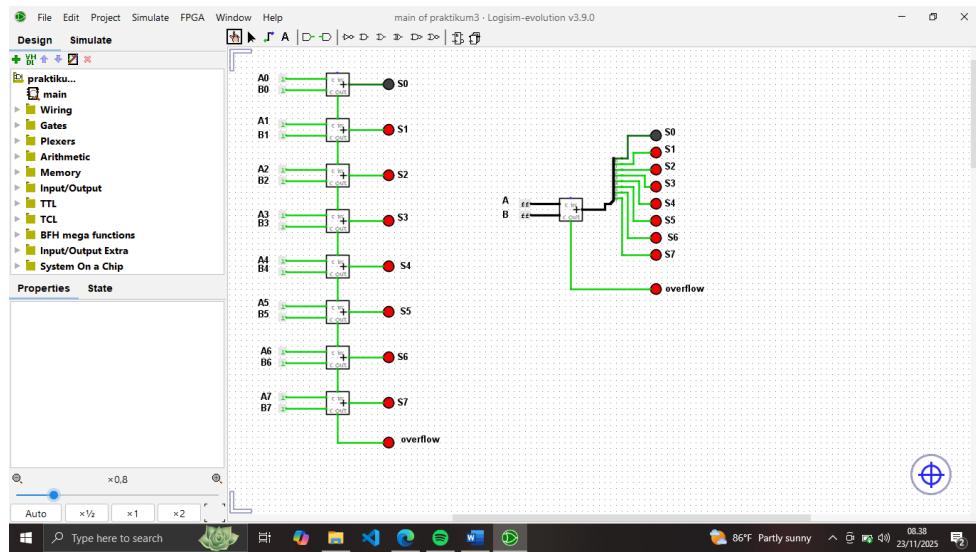

- Aritmatika

Pada rangkaian ini terdapat dua masukan utama (A dan B), masing-masing terdiri dari 8 bit. Kedua input tersebut terhubung langsung ke modul adder, sehingga proses penjumlahan bilangan biner dilakukan secara otomatis oleh blok aritmatika. Adder akan melakukan penjumlahan bit per bit dari posisi terendah hingga tertinggi dengan mempertimbangkan carry-in di dalam blok. Hasil dari proses penjumlahan ini ditampilkan melalui 8 keluaran S0 - S7 yang menunjukkan nilai sum dari bit 0 - 7. Sedangkan carry terakhir dari hasil penjumlahan bit tertinggi ditampilkan melalui LED overflow sebagai indikator terjadinya melebihi batas hasil penjumlahan.

- Tabel pengujian

| A        | B        | C-in | Sum      | C-out |

|----------|----------|------|----------|-------|

| 00000000 | 00000000 | 0    | 00000000 | 0     |

| 00001101 | 00000111 | 0    | 00010100 | 0     |

| 10101010 | 01010101 | 0    | 11111111 | 0     |

| 11111111 | 11111111 | 0    | 11111110 | 1     |

| 10011001 | 11001100 | 1    | 01100110 | 1     |

Pada pengujian pertama, input A dan B bernilai 00000000 dan C-out bernilai 0, yang menandakan tidak terjadi penambahan nilai maupun kelebihan hasil. Pengujian kedua menggunakan nilai acak 00001101 dan 00000111 dengan C-in 0 menghasilkan sum 00010100 dan C-out bernilai 0, sesuai dengan hasil penjumlahan biner tanpa overflow. Pengujian ketiga menggunakan pola komplementer 10101010 dan 01010101 menghasilkan sum 11111111 dengan C-out bernilai 0, membuktikan bahwa rangkaian dapat menangani semua

kombinasi bit dan tetap memberikan keluaran yang benar. Pada pengujian keempat, kedua input berada pada nilai maksimum 11111111, dan hasil penjumlahan menghasilkan 11111110 dengan C-out 1, yang menunjukkan bahwa total penjumlahan melebihi kapasitas 8 bit sehingga terjadi overflow. Pada pengujian kelima dengan nilai 10011001 dan 11001100 dengan C-in 1 menghasilkan sum 01100110 dengan C-out 1, yang menunjukkan bahwa rangkaian mampu memproses C-in dan eksternal secara akurat.

## 2. Comparator

Dari hasil praktikum 8-bit comparator yang berfungsi untuk membandingkan dua bilangan biner 8-bit (A dan B). Proses pembandingannya dilakukan secara bertahap mulai dari bit yang paling signifikan (A7 dan B7) sampai bit paling rendah (A0 dan B0). Setiap pasangan bit  $A_i$  dan  $B_i$  diproses untuk mengetahui apakah  $A_i$  lebih besar dari  $B_i$ , lebih kecil, atau sama dengan. Untuk mengetahui kesamaan bit yang digunakan logika XNOR. Sinyal kesamaan ini kemudian diteruskan sebagai informasi penyebaran ke tahap berikutnya. Hasil perbandingan akan ditentukan berdasarkan tiga kondisi yang saling eksklusif  $A = B$ ,  $A > B$ , atau  $A < B$ . Kondisi  $A = B$  akan bernilai 1 jika seluruh bit dari A dan B sama, karena sinyal kesamaan dari bit 7 hingga bit 0 di-AND secara keseluruhan. Sedangkan kondisi  $A > B$  dan  $A < B$  ditentukan dengan melihat bit pertama dari sisi MSB yang berbeda. Jika bit-bit yang lebih tinggi masih sama, keputusan perbandingan baru diambil pada bit berikutnya yang tidak sama. Rangkaian menghasilkan dua output utama yaitu  $A > B$  dan  $A <$

B. Jika kedua output bernilai 0, maka dapat disimpulkan bahwa A dan B memiliki nilai yang sama.

#### **1.4 Kesimpulan**

Berdasarkan hasil praktikum, rangkaian 8-bit adder dan comparator keduanya dapat berkerja sesuai fungsinya. 8-bit adder mampu melakukan operasi penjumlahan dua bilangan biner 8 bit dengan tepat melalui mekanisme ripple carry, di mana setiap full adder menangani satu bit penjumlahan dan meneruskan carry ke tahap berikutnya hingga menghasilkan output sum dan carry out yang benar. Sementara itu, 8-bit comparator dapat membandingkan dua bilangan biner 8 bit secara akurat melalui proses perbandingan bertahap mulai dari bit yang paling signifikan sampai bit paling rendah untuk menentukan apakan  $A > B$ ,  $A = B$ ,  $A < B$ . Hasil pengujian dari kedua rangkaian menunjukkan bahwa logika digital yang diterapkan berfungsi dengan benar dan mampu menghasilkan output yang sesuai dengan teori, sehingga rangkaian yang dibuat dapat dapat berjalan secara optimal.