## **PRAKTIKUM PENGANTAR SISTEM DIGITAL**

**Dosen: Arif Rifa'i Dwiyanto, ST., MTI**

### **MULTIPLEXER DAN DEMULTIPLEXER**

**Disusun oleh:**

**Pingky Nanda Rahmadhani**

**202410715036**

**F3A6**

**LAPORAN PRAKTIKUM PENGANTAR SISTEM

DIGITAL

PROGRAM STUDI INFORMATIKA – FAKULTAS ILMU

KOMPUTER

UNIVERSITAS BHAYANGKARA JAKARTA RAYA

2025**

# BAB I

## PENDAHULUAN

### 1.1 Tujuan

- Mahasiswa memahami konsep kerja Multiplexer (MUX) dan Demultiplexer (DEMUX).

- Mahasiswa mampu merancang dan mensimulasikan MUX dan DEMUX menggunakan Logisim.

- Mempelajari proses penggabungan MUX dan DEMUX.

### 1.2 Alat dan Bahan

- Laptop/PC dengan aplikasi Logisim Evolution terinstal

- Modul panduan praktikum

- Buku catatan

### 1.3 Langkah-Langkah Kerja

#### A. Merancang 8-to-1 Multiplexer

- Tambahkan 8 Constant untuk input  $I_0, I_1, I_2, I_3, I_4, I_5, I_6, I_7$ .

- Tambahkan 3 Constant untuk select lines  $S_0, S_1$ , dan  $S_2$ .

- Gunakan kombinasi gerbang AND, OR, dan NOT sesuai ekspresi logika.

- Tambahkan LED untuk melihat hasil output  $Y$ .

- Simulasikan rangkaian dengan berbagai kombinasi input dan select lines.

- Input :  $I_0, I_1, I_2, I_3, I_4, I_5, I_6, I_7$

- Select Lines :  $S_0, S_1, S_2$

- Output : Y

- Ekspresi Logika Output :

$$Y = (S_2' \cdot S_1' \cdot S_0' \cdot I_0) + (S_2' \cdot S_1' \cdot S_0 \cdot I_1) + (S_2' \cdot S_1 \cdot S_0' \cdot I_2) + (S_2' \cdot S_1 \cdot S_0 \cdot I_3) + (S_2 \cdot S_1' \cdot S_0' \cdot I_4) + (S_2 \cdot S_1' \cdot S_0 \cdot I_5) + (S_2 \cdot S_1 \cdot S_0' \cdot I_6) + (S_2 \cdot S_1 \cdot S_0 \cdot I_7)$$

- Tabel kebenaran :

| S2 | S1 | S0 | Y              |

|----|----|----|----------------|

| 0  | 0  | 0  | I <sub>0</sub> |

| 0  | 0  | 1  | I <sub>1</sub> |

| 0  | 1  | 0  | I <sub>2</sub> |

| 0  | 1  | 1  | I <sub>3</sub> |

| 1  | 0  | 0  | I <sub>4</sub> |

| 1  | 0  | 1  | I <sub>5</sub> |

| 1  | 1  | 0  | I <sub>6</sub> |

| 1  | 1  | 1  | I <sub>7</sub> |

## B. Merancang 1-to-8 Demultiplexer

- Tambahkan 1 Constant untuk input I.

- Tambahkan 3 Constant untuk select lines S0, S1, dan S2.

- Gunakan kombinasi gerbang AND dan NOT sesuai ekspresi logika untuk setiap output.

- Hubungkan setiap output ke LED.

- Simulasikan rangkaian dengan berbagai kombinasi select lines dan input I.

- Input : I

- Select Lines : S0, S1, S2

- Output : Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7

- Ekspresi Logika Output :

$$Y_0 = S_0' \cdot S_1' \cdot S_2' \cdot I$$

$$Y_1 = S_0' \cdot S_1' \cdot S_2 \cdot I$$

$$Y_2 = S_0' \cdot S_1 \cdot S_2' \cdot I$$

$$Y_3 = S_0' \cdot S_1 \cdot S_2 \cdot I$$

$$Y_4 = S_0 \cdot S_1' \cdot S_2' \cdot I$$

$$Y_5 = S_0 \cdot S_1' \cdot S_2 \cdot I$$

$$Y_6 = S_0 \cdot S_1 \cdot S_2' \cdot I$$

$$Y_7 = S_0 \cdot S_1 \cdot S_2 \cdot I$$

- Tabel Kebenaran :

| Select Lines |    |    | Output |    |    |    |    |    |    |    |

|--------------|----|----|--------|----|----|----|----|----|----|----|

| S2           | S1 | S0 | Y0     | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

| 0            | 0  | 0  | 1      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0            | 0  | 1  | 0      | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0            | 1  | 0  | 0      | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 0            | 1  | 1  | 0      | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| 1            | 0  | 0  | 0      | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| 1            | 0  | 1  | 0      | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 1            | 1  | 0  | 0      | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 1            | 1  | 1  | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

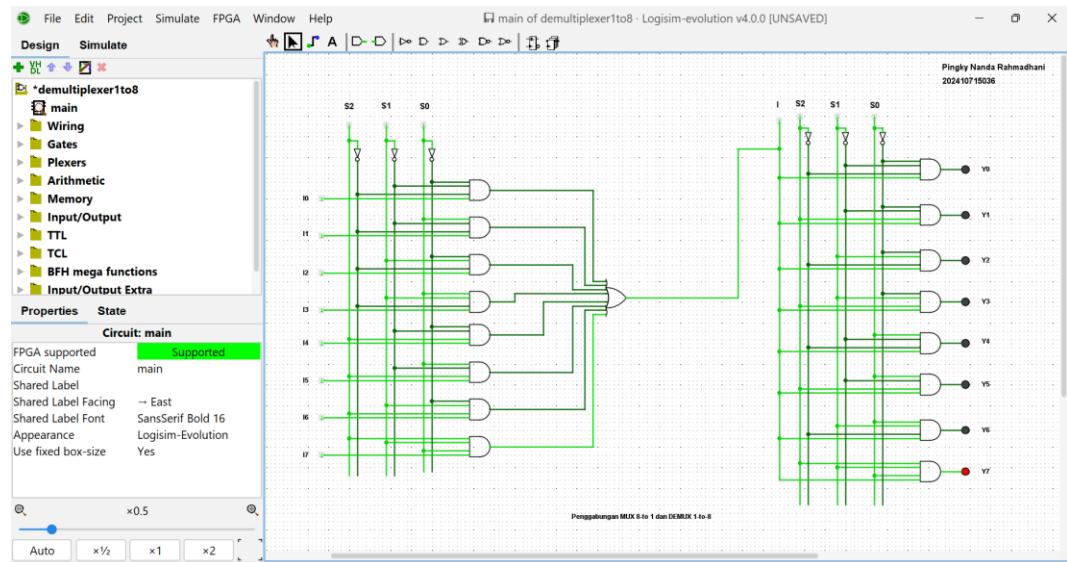

### C. Gabungkan Multiplexer dan Demultiplexer

- Buat Multiplexer 8x1 seperti pada langkah sebelumnya.

- Buat Demultiplexer 1x8 sesuai langkah sebelumnya.

- Hubungkan output dari Multiplexer ke input Demultiplexer.

- Gunakan select line yang sama untuk MUX dan DEMUX.

- Tambahkan switch sebagai input ke Multiplexer dan LED untuk output Demultiplexer.

- Simulasikan rangkaian untuk memverifikasi fungsi Multiplexer dan Demultiplexer secara bersamaan

## BAB II

### PEMBAHASAN SIMULASI

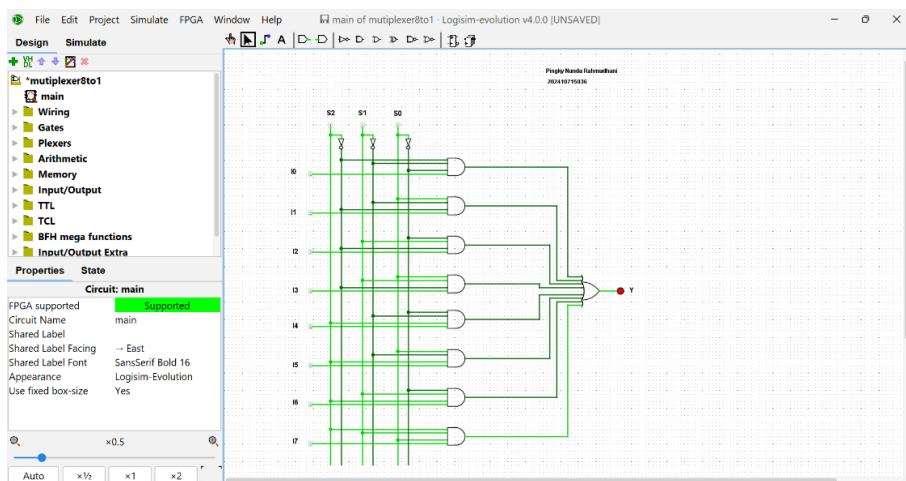

#### 2.1 Multiplexer 8-to-1

Multiplexer adalah suatu rangkaian logika kombinasi yang berfungsi untuk memilih satu sinyal input dari beberapa input yang tersedia untuk diteruskan ke satu output. Pemilihan ini dikendalikan oleh sinyal kontrol yang disebut select lines, yang menentukan jalur input mana yang aktif pada suatu waktu. Rangkaian pada gambar menunjukkan implementasi multiplexer 8-to1 menggunakan gerbang dasar AND, NOT, dan OR. Terdiri dari 8 input data (I0-I7), tiga select lines (S0, S1, S2), dan satu output Y. Pada rangkaian, setiap select lines tidak hanya disalurkan dalam bentuk aslinya, tetapi juga melalui gerbang NOT untuk menghasilkan sinyal yang terinversi. Hal ini diperlukan agar setiap gerbang AND menerima kombinasi select lines yang sesuai dengan pola pemilihan input tertentu.

Setiap gerbang AND mewakili satu kombinasi select lines Misalnya, gerbang AND pertama aktif ketika select lines dalam kombinasi 000, sehingga input I0 diteruskan ke output. Gerbang AND berikutnya aktif untuk kombinasi 001, lalu 010, dan seterusnya hingga kombinasi 111 pada gerbang AND terakhir. Dengan demikian, hanya satu gerbang AND yang aktif pada suatu waktu sesuai dengan kombinasi select lines yang terpilih. Seluruh keluaran dari delapan gerbang AND kemudian digabungkan menggunakan gerbang OR. Karena hanya satu gerbang AND yang aktif, gerbang OR meneruskan sinyal input yang dipilih ke output Y.

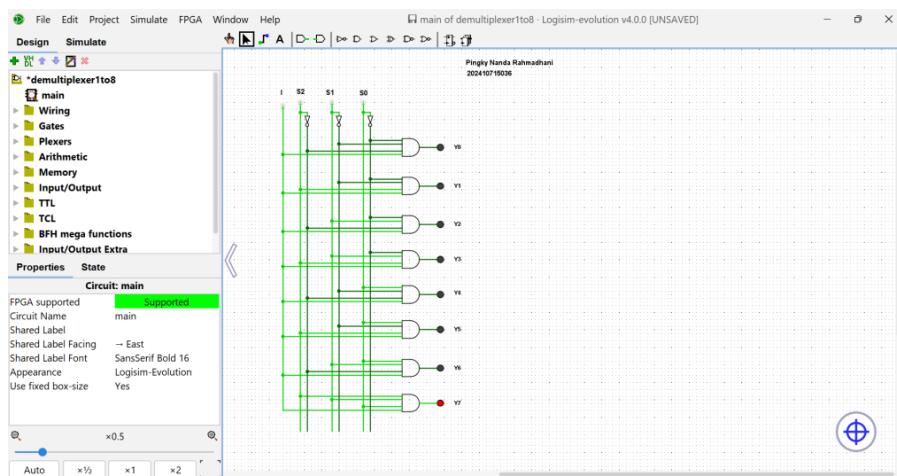

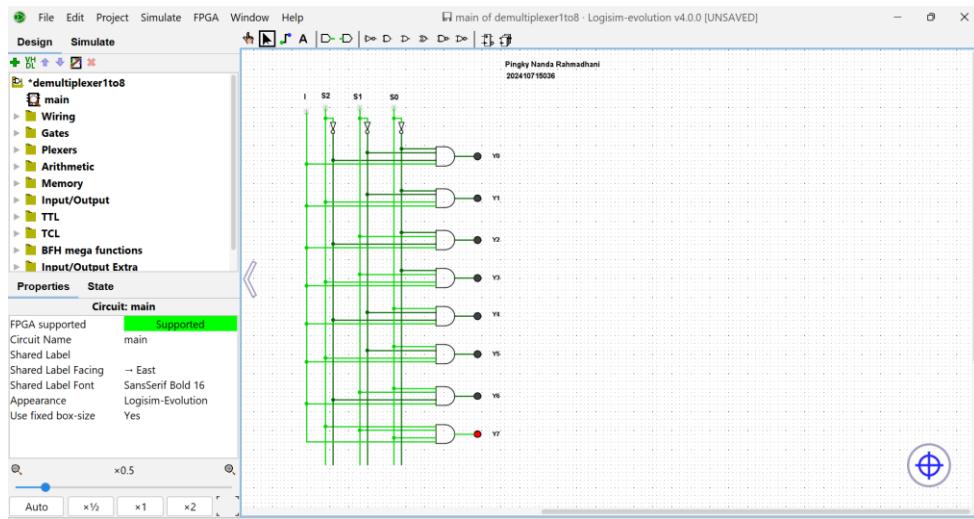

## 2.2 Demultiplexer 1-to-8

Demultiplexer merupakan rangkaian logika kombinasi yang berfungsi untuk menyalurkan satu input menuju salah satu dari beberapa output berdasarkan kondisi select lines. Jika multiplexer memilih satu input untuk dikirim ke satu output, maka demultiplexer melakukan proses kebalikannya yaitu satu input dapat diarahkan menuju salah satu dari banyak output. Pada gambar menunjukkan implementasi demultiplexer 1-to-8 yang dibangun menggunakan gerbang logika AND dan NOT. Rangkaian ini memiliki satu input data (I), tiga select lines (S0, S1, S2), dan delapan keluaran (Y0 sampai Y7).

Ketiga select lines digunakan untuk menentukan ke output mana sinyal input akan diteruskan. Masing-masing select line dibagi ke beberapa cabang, dan beberapa sinyal melewati gerbang NOT untuk menghasilkan sinyal terbalik, sehingga seluruh kombinasi select lines bisa terpenuhi sesuai kode biner. Setiap gerbang AND mewakili satu jalur output dan hanya akan menghasilkan nilai tinggi jika input I bernilai satu dan select lines menunjukkan kombinasi yang sesuai dengan output tersebut. Misalnya, output Y0 aktif ketika select lines bernilai 000, Y1 aktif untuk kombinasi 001, Y2 untuk 010, dan seterusnya hingga Y7 yang aktif pada kombinasi 111. Dengan demikian, pada satu waktu hanya satu gerbang AND yang mengizinkan sinyal input diteruskan ke output tertentu, sementara output lainnya tetap pada level logika rendah.

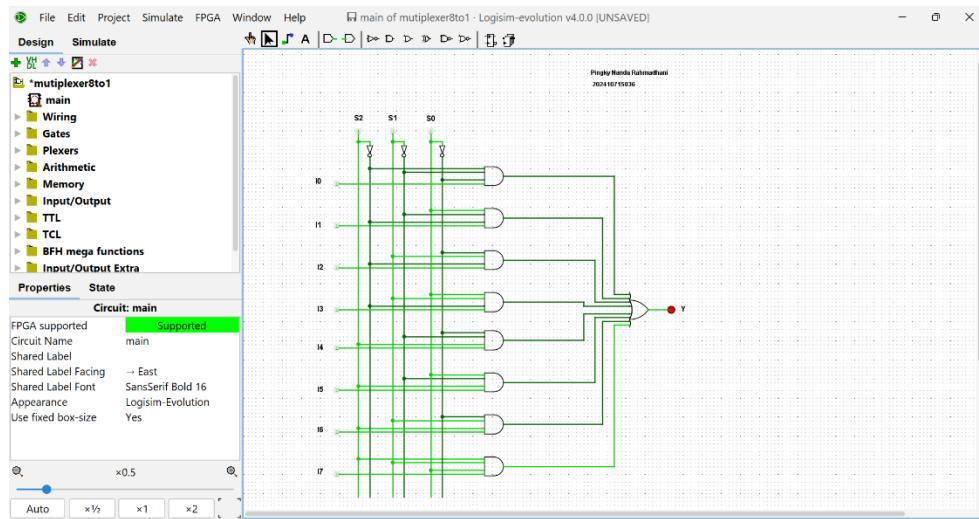

### 2.3 Gabungan Multiplexer dan Demultiplexer

Pada gambar tersebut menunjukkan sebuah rangkaian yang menggabungkan fungsi Multiplexer 8-to-1 dan Demultiplexer 1-to-8. Penggabungan ini dilakukan dengan cara menghubungkan output tunggal MUX ke input tunggal DEMUX, sehingga sinyal yang dipilih oleh Multiplexer dapat didistribusikan kembali oleh Demultiplexer ke salah satu dari delapan output.

## **BAB III**

### **KESIMPULAN**

Pada praktikum ini, Multiplexer (MUX) 8-to-1 bekerja dengan memilih satu dari delapan input berdasarkan kombinasi tiga select lines (S2, S1, S0). Pengujian menunjukkan bahwa hanya input yang sesuai dengan nilai select lines yang diteruskan ke output, sehingga membuktikan fungsi utama MUX sebagai rangkaian pemilih data. Demultiplexer (DEMUX) 1-to-8 berfungsi mendistribusikan satu sinyal input ke salah satu dari delapan output sesuai dengan nilai select lines. Hasil praktikum memperlihatkan bahwa hanya output yang cocok dengan kombinasi select lines yang aktif, sedangkan output lainnya tetap tidak terpengaruh.

Pada rangkaian gabungan MUX dan DEMUX, sinyal yang dipilih oleh MUX dapat dikirim melalui satu jalur dan kemudian diarahkan kembali ke output tertentu oleh DEMUX dengan menggunakan select lines yang sama. Pengujian membuktikan bahwa sistem gabungan ini dapat mengirimkan dan mendistribusikan sinyal secara tepat, menunjukkan bagaimana MUX dan DEMUX dapat bekerja bersama dalam proses pengalihan dan pengaturan data digital. Secara keseluruhan, praktikum ini menyimpulkan bahwa MUX dan DEMUX sangat penting dalam sistem digital karena mampu menghemat jalur, mengatur aliran data, serta mempermudah proses pemilihan dan penyaluran sinyal secara efisien dan terkontrol.