## **PRAKTIKUM PENGANTAR SISTEM DIGITAL**

**Dosen: Arif Rifa'i Dwiyanto, ST., MTI**

### **RANGKAIAN SEKUENSIAL (FLIP-FLOP)**

**Disusun oleh:**

**Pingky Nanda Rahmadhani**

**202410715036**

**F3A6**

**LAPORAN PRAKTIKUM PENGANTAR SISTEM

DIGITAL

PROGRAM STUDI INFORMATIKA – FAKULTAS ILMU

KOMPUTER

UNIVERSITAS BHAYANGKARA JAKARTA RAYA

2025**

## BAB I

### PENDAHULUAN

#### 1.1 Tujuan

- Mahasiswa memahami konsep rangkaian sequensial

- Mahasiswa mampu merancang dan mensimulasikan flip-flop dasar (SR, D, dan JK).

#### 1.2 Alat dan Bahan

- Laptop/PC dengan aplikasi Logisim Evolution terinstal

- Modul panduan praktikum

- Buku catatan

#### 1.3 Langkah-Langkah Kerja

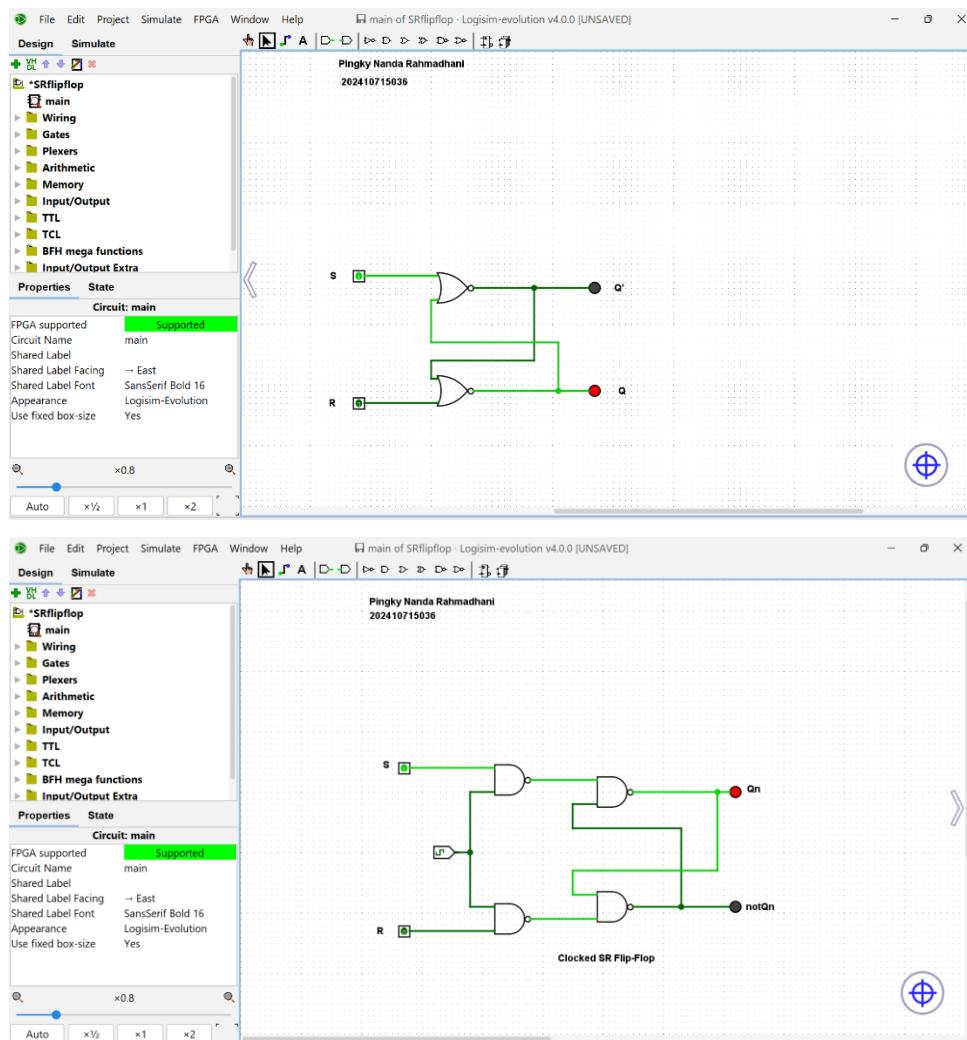

##### 1.3.1 Membuat Rangkaian SR (Set-Reset) Flip-Flop

Langkah-langkah Pembangunan Rangkaian SR Flip-Flop pada Logisim:

1. Meletakkan dua gerbang NOR/NAND pada area kerja.

2. Menghubungkan output dari masing-masing gerbang ke salah satu input gerbang lainnya sehingga terbentuk hubungan umpan balik.

3. Menghubungkan input pin S (Set) dan R (Reset) ke masing-masing NOR/NAND.

4. Menambahkan indicator berupa LED pada output Q dan Q'

5. Memastikan semua koneksi telah tersambung dengan benar.

6. Melakukan pengujian dengan memberikan berbagai kombinasi logika pada input S dan R seperti (0,0), (1,0), (0,1), dan (1,1).

7. Mengamati kondisi keluaran Q dan Q' berdasarkan pada tabel kebenaran.

| Input |    |   | Output    | State     |

|-------|----|---|-----------|-----------|

| CLK   | SR | R | Q         |           |

| x     | 0  | 0 | No Change | Previous  |

| ↑     | 0  | 1 | 0         | Reset     |

| ↑     | 1  | 0 | 1         | Set       |

| ↑     | 1  | 1 | -         | Forbidden |

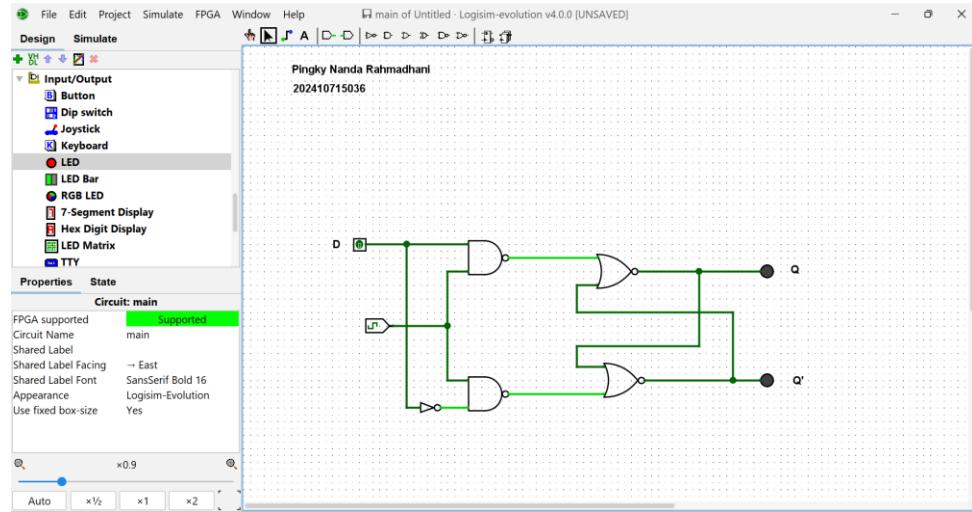

### 1.3.2 Membuat Rangkaian D Flip-Flop

Langkah-langkah Pembangunan Rangkaian D Flip-Flop pada Logisim:

1. Tambahkan gerbang NOT dan satu rangkaian SR Flip-Flop pada area kerja.

2. Menghubungkan input D ke jalur S (Set) dan D' melalui gerbang NOT ke jalur R (Reset) pada SR Flip-Flop.

3. Menambahkan output LED pada terminal Q dan Q' untuk memudahkan pengamatan hasil keluaran.

4. Memeriksa ulang seluruh koneksi agar tidak terdapat jalur yang terputus atau salah sambung.

5. Melakukan simulasi dengan memberikan variasi nilai logika pada input D serta mengamati perubahan keluaran Q dan Q'.

6. Membandingkan hasil pengamatan berdasarkan tabel kebenaran.

| Input |       |       | Output |    |

|-------|-------|-------|--------|----|

| D     | Reset | Clock | Q      | Q' |

| 0     | 0     | 0     | 0      | 1  |

| 0     | 0     | 1     | 0      | 1  |

| 0     | 1     | 0     | 0      | 1  |

| 0     | 1     | 1     | 0      | 1  |

| 1     | 0     | 0     | 0      | 1  |

| 1     | 0     | 1     | 1      | 0  |

| 1     | 1     | 0     | 0      | 1  |

| 1     | 1     | 1     | 0      | 1  |

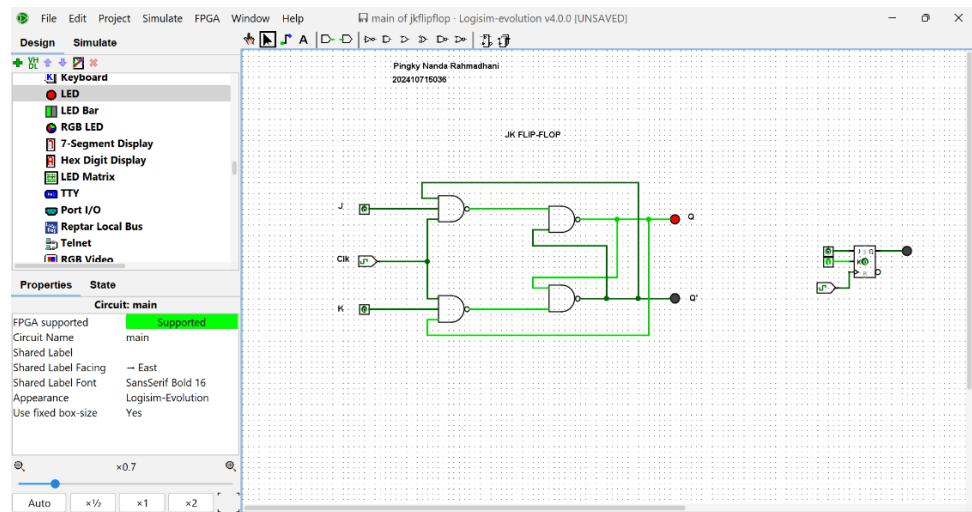

### 1.3.3 Membuat Rangkaian JK Flip-Flop

Langkah-langkah Pembangunan Rangkaian JK Flip-Flop pada Logisim:

1. Bangun rangkaian SR Flip-Flop seperti langkah kerja sebelumnya.

2. Tambahkan dua gerbang AND untuk membentuk sinyal Set dan Reset yang terkontrol oleh clock.

3. Pada bagian Set, hubungkan input J ke gerbang AND (3-input)

- Input kedua gerbang AND dihubungkan ke output Q' dari SR Flip-Flop.

- Input ketiga menerima sinyal Clock.

- Output dari AND ini menjadi sinyal S untuk SR Flip-Flop.

4. Pada bagian Reset, hubungkan input K ke gerbang AND (3-input)

- Input kedua gerbang AND dihubungkan ke output Q dari SR Flip-Flop

- Input ketiga menerima sinyal Clock.

- Output dari AND ini menjadi sinyal R untuk SR Flip-Flop.

5. Berikan satu sinyal Clock yang sama ke kedua gerbang AND agar perubahan state hanya terjadi saat clock aktif.

6. Memastikan seluruh koneksi telah tersambung dengan benar.

7. Melakukan pengujian berdasarkan tabel kebenaran.

| J | K | CLK | Q | Q' |

|---|---|-----|---|----|

| 0 | 0 | 0   | 0 | 1  |

| 0 | 0 | 1   | 0 | 1  |

| 0 | 1 | 0   | 1 | 0  |

| 0 | 1 | 1   | 1 | 0  |

| 1 | 0 | 0   | 0 | 1  |

| 1 | 0 | 1   | 0 | 1  |

| 1 | 1 | 0   | 1 | 0  |

| 1 | 1 | 1   | 1 | 0  |

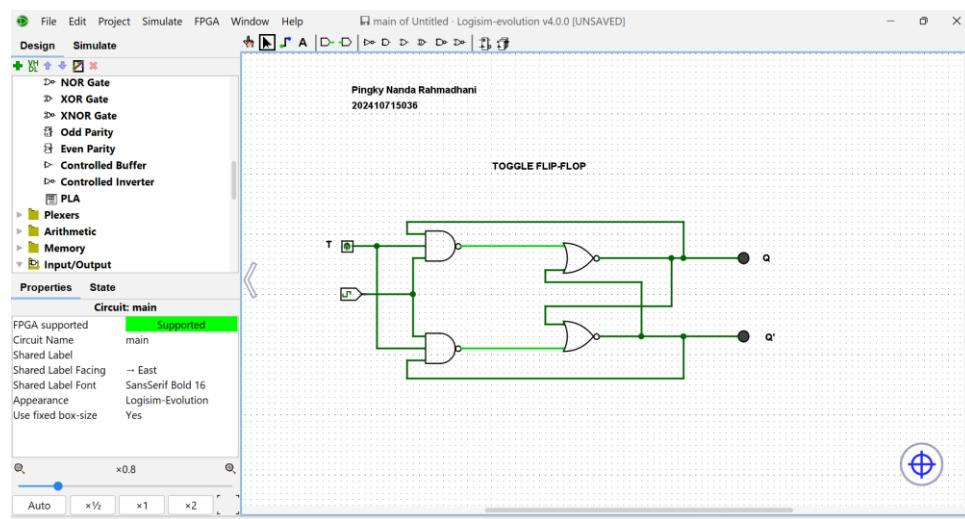

#### 1.3.4 Membuat Rangkaian T (Toggle) Flip-Flop

Langkah-langkah Pembangunan Rangkaian Toggle Flip-Flop pada Logisim:

1. Buat SR Flip-Flop (SR Latch)

- Meletakkan dua gerbang NOR secara vertikal.

- Sambungkan salah satu input NOR atas ke output NOR bawah.

- Sambungkan salah satu input NOR bawah ke output NOR atas.

- Ouput NOR atas menjadi Q dan ouput NOR bawah menjadi Q'.

2. Buat bagian Logika AND (Pembentuk S dan R untuk T Flip-Flop)

- Tambahkan dua gerbang AND dengan 3-input untuk menghasilkan S dan R.

- Hubungkan T dan CLK ke kedua gerbang AND.

- Input ketiga untuk masing-masing AND

- Hubungkan AND atas ke Q'

- Hubungkan AND bawah ke Q

3. Hubungkan Output AND ke SR Latch

- Output AND atas dihubungkan ke input kosong pada NOR atas (S)

- Output AND bawah dihubungkan ke input kosong pada NOR bawah (R).

4. Tambahkan input dan Output

- Gunakan switch untuk input T dan CLK.

- Pasang LED untuk output Q dan Q'

5. Memastikan seluruh koneksi telah tersambung dengan benar dan lakukan pengujian berdasarkan tabel kebenaran.

| T | Q(n) | Q(n+1) |

|---|------|--------|

| 0 | 0    | 0      |

| 0 | 1    | 1      |

| 1 | 0    | 1      |

| 1 | 1    | 0      |

## BAB II

### PEMBAHASAN SIMULASI

#### 2.1 Rangkaian SR Flip-Flop

Rangkaian SR Fli-Flop merupakan rangkaian logika sekuensial yang dirancang untuk menyimpan satu bit data. SR Flip-Flop dibangun menggunakan dua gerbang logika NOR dan NAND yang saling terhubung secara umpan balik. Pada simulasi Logisim, input S (Set) digunakan untuk mengatur keluaran Q menjadi logika 1, sementara input R (Reset) digunakan untuk mengatur keluaran Q menjadi logika 0. Keluaran  $Q'$  selalu bernilai kebalikan dari Q, sehingga menunjukkan sifat penyimpanan keadaan pada flip-flop. Hasil simulasi menunjukkan bahwa SR Fli-Flop mampu mempertahankan kondisi terakhirnya ketika kedua input S dan R bernilai 0. Namun, terdapat kondisi terlarang saat S dan R bernilai 1 secara bersamaan karena menyebabkan keluaran tidak terdefinisi.

## 2.2 Rangkaian D Flip-Flop

Rangkaian D Flip-Flop merupakan pengembangan dari SR Flip-Flop yang dirancang untuk menghilangkan kondisi terlarang. D Flip-Flop memiliki satu input utama yaitu D (Data) serta dikendalikan oleh sinyal clock. Pada simulasi Logisim, nilai input D akan disimpan dan diteruskan ke keluaran Q saat terjadi perubahan clock, sedangkan Q' selalu menjadi kebalikan dari Q. Hal ini memungkinkan D Flip-Flop menyimpan data secara lebih stabil dan terkontrol. Hasil simulasi menunjukkan bahwa keluaran Q hanya berubah mengikuti nilai D ketika clock aktif, dan mempertahankan nilai sebelumnya saat clock tidak aktif.

## 2.3 Rangkaian JK Flip-Flop

Rangkaian JK Flip-Flop pada logisim merupakan pengembangan dari SR Flip-Flop yang dirancang untuk menghilangkan kondisi terlarang. JK Flip-Flop memiliki dua input utama yaitu J dan K serta dikendalikan oleh sinyal clock. Pada simulasi Logisim, Ketika J = 1 dan K = 0, keluaran Q akan di set menjadi 1,

sedangkan saat  $J = 0$  dan  $K = 1$ , keluaran  $Q$  akan direset menjadi 0. Jika  $J$  dan  $K$  bernilai 0, maka keluaran akan mempertahankan kondisi sebelumnya (hold).

Hasil simulasi menunjukkan bahwa ketika  $J$  dan  $K$  sama-sama bernilai 1 dan clock aktif, JK flip-flop akan melakukan toggle, yaitu keluaran  $Q$  berubah ke kondisi kebalikannya. Keluaran  $Q$  selalu bernilai kebalikan dari  $Q'$ , sehingga memperlihatkan sifat penyimpanan dan perubahan keadaan yang terkontrol. Melalui simulasi di Logisim, karakteristik jera JK flip-flop dapat dipahami dengan jelas, terutama dalam mengamati respon keluaran terhadap berbagai kombinasi input dan sinyal clock pada rangkaian sekuensial.

## 2.4 Rangkaian T Flip-Flop

Rangkaian Toggle Flip-Flop merupakan rangkaian logika sekuensial yang digunakan untuk mengubah kondisi keluaran secara bergantian. T Flip-Flop memiliki satu input utama yaitu  $T$  (Toggle) dan biasanya dikendalikan oleh sinyal clock. Pada simulasi Logisim, Ketika input  $T$  bernilai 1 dan terjadi pulsa clock, keluaran  $Q$  akan berubah dari 0 menjadi 1 atau dari 1 menjadi 0. Sebaliknya, jika input  $T$  bernilai 0, maka keluaran  $Q$  akan mempertahankan nilai sebelumnya meskipun clock aktif. Hasil simulasi menunjukkan bahwa T Flip-Flop sangat efektif untuk aplikasi pencacah (counter) karena  $Q'$  selalu bernilai kebalikan dari  $Q$ , sehingga memperlihatkan sifat penyimpanan dan perubahan keadaan secara terkontrol.

## **BAB III**

### **KESIMPULAN**

Berdasarkan praktikum yang telah dilakukan, dapat disimpulkan bahwa rangkaian sekuensial berbasis flip-flop SR, D, JK, dan Toggle (T) merupakan komponen dasar penyimpanan data pada sistem digital yang bekerja berdasarkan perubahan kondisi input dan sinyal clock. Setiap jenis flip-flop memiliki karakteristik kerja yang berbeda, di mana SR flip-flop mampu menyimpan satu bit data namun memiliki kondisi terlarang, D flip-flop menjamin kestabilan dengan menangkap input D saat clock aktif, JK flip-flop mengatasi kelemahan SR flip-flop dengan menyediakan fungsi toggle, serta T flip-flop menghasilkan perubahan keluaran secara bergantian setiap pulsa clock ketika input aktif.

Melalui simulasi menggunakan Logisim, prinsip kerja masing-masing flip-flop dapat diamati secara langsung, mulai dari perubahan keluaran, kondisi penyimpanan (hold), hingga respon terhadap sinyal clock. Praktikum ini memperkuat pemahaman mengenai konsep memori, sinkronisasi, dan pengendalian data dalam rangkaian digital. Dengan demikian, flip-flop sangat berperan penting sebagai elemen dasar dalam perancangan sistem digital seperti register, counter, dan rangkaian kontrol.