## **PRAKTIKUM PENGANTAR SISTEM DIGITAL**

**Dosen: Arif Rifa'i Dwiyanto, ST., MTI**

### **RANGKAIAN HALF ADDER & FULL ADDER**

**Disusun oleh:**

**Pingky Nanda Rahmadhani**

**202410715036**

**F3A6**

**LAPORAN PRAKTIKUM PENGANTAR SISTEM

DIGITAL

PROGRAM STUDI INFORMATIKA – FAKULTAS ILMU

KOMPUTER

UNIVERSITAS BHAYANGKARA JAKARTA RAYA

2025**

# **BAB I**

## **PENDAHULUAN**

### **1.1 Tujuan**

- Mahasiswa memahami konsep rangkaian kombinasi.

- Mahasiswa mampu membangun rangkaian Half Adder dan Full Adder menggunakan Logisim.

### **1.2 Alat dan Bahan**

- Laptop/PC dengan aplikasi Logisim Evolution terinstal

- Modul panduan praktikum

- Buku catatan

### **1.3 Langkah-Langkah Kerja**

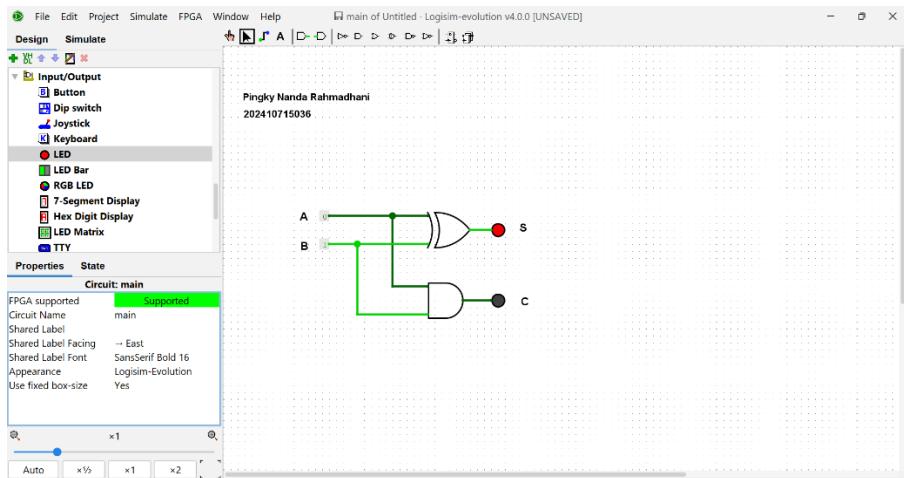

#### **A. Membuat Half Adder**

1. Bangun rangkaian Half Adder dengan ekspresi logika berikut:

- $S=A \oplus B$  (*XOR*)

- $C=A \cdot B$  (*AND*)

2. Hubungkan input A dan B menggunakan Constant.

3. Tambahkan LED pada output S (Sum) dan C (Carry).

Tabel Kebenaran:

| Input          |   | Output |       |

|----------------|---|--------|-------|

| A              | B | SUM    | CARRY |

| 0              | 0 | 0      | 0     |

| 0              | 1 | 1      | 0     |

| 1              | 0 | 1      | 0     |

| 1              | 1 | 0      | 1     |

| Gerbang Logika |   | XOR    | AND   |

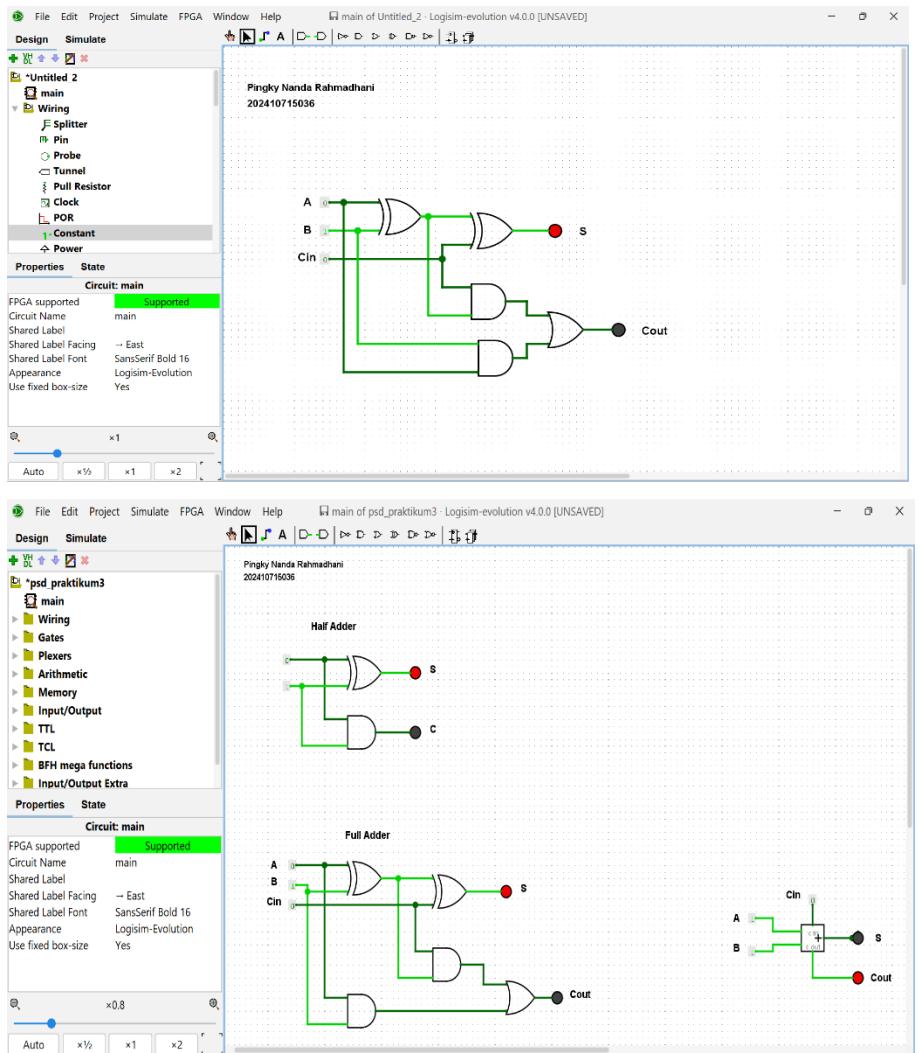

## B. Membuat Full Adder

1. Bangun rangkaian Full Adder dengan ekspresi logika berikut:

- $S = (A \oplus B) \oplus C_{in}$

- $C_{out} = (A \cdot B) + ((A \oplus B) \cdot C_{in})$

2. Gunakan dua gerbang XOR, dua gerbang AND, dan satu gerbang OR untuk membangun rangkaian.

3. Hubungkan input A, B, dan Cin menggunakan Constant.

4. Tambahkan LED pada output S (sum) dan C<sub>out</sub> (carry out).

Tabel Kebenaran:

| Input          |   | Output          |                              |                                             |

|----------------|---|-----------------|------------------------------|---------------------------------------------|

| A              | B | C <sub>IN</sub> | SUM                          | C <sub>OUT</sub>                            |

| 0              | 0 | 0               | 0                            | 0                                           |

| 0              | 0 | 1               | 1                            | 0                                           |

| 0              | 1 | 0               | 1                            | 0                                           |

| 0              | 1 | 1               | 0                            | 1                                           |

| 1              | 0 | 0               | 1                            | 0                                           |

| 1              | 0 | 1               | 0                            | 1                                           |

| 1              | 1 | 0               | 0                            | 1                                           |

| 1              | 1 | 1               | 1                            | 1                                           |

| Gerbang Logika |   |                 | $(A \oplus B) \oplus C_{in}$ | $(A \cdot B) + ((A \oplus B) \cdot C_{in})$ |

### C. Simulasi

- Uji rangkaian dengan berbagai kombinasi input

- Catat hasil dalam tabel berikut:

| A | B | C <sub>in</sub> | S | C <sub>out</sub> |

|---|---|-----------------|---|------------------|

| 0 | 0 | 0               | 0 | 0                |

| 0 | 0 | 1               | 1 | 0                |

| 0 | 1 | 0               | 1 | 0                |

| 0 | 1 | 1               | 0 | 1                |

| 1 | 0 | 0               | 1 | 0                |

| 1 | 0 | 1               | 0 | 1                |

| 1 | 1 | 0               | 0 | 1                |

| 1 | 1 | 1               | 1 | 1                |

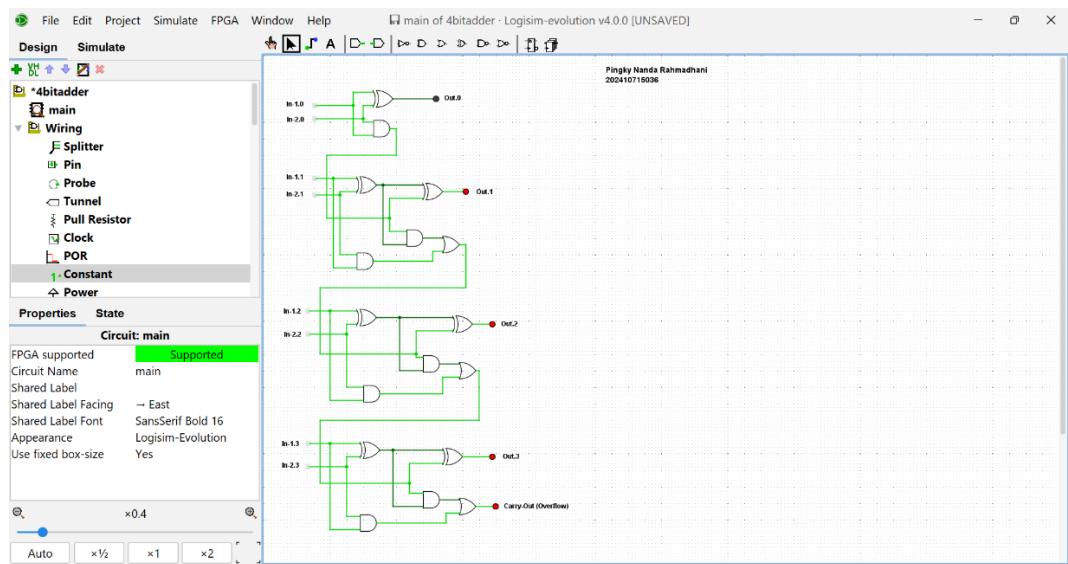

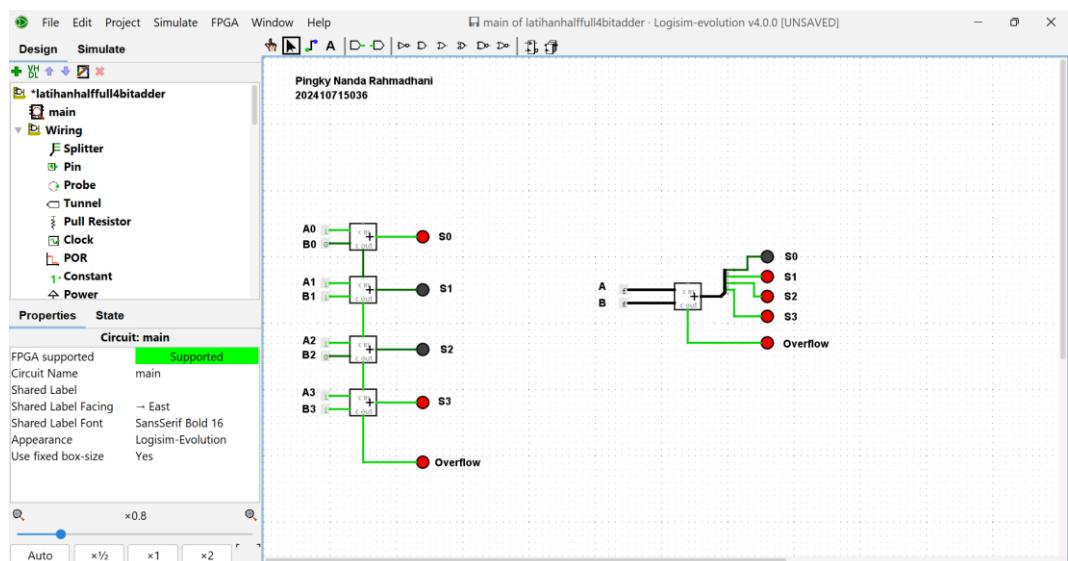

## 1) 4-bit Adder

### Menggunakan Komponen Aritmatika

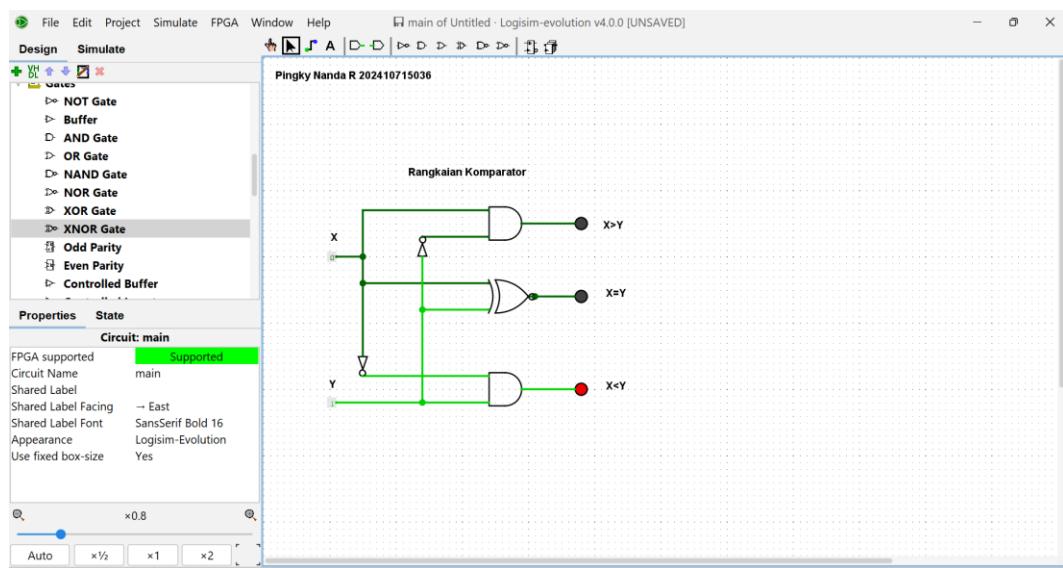

## 2) Rangkaian Komparator

Sebuah rangkaian Comparator berfungsi membandingkan dua buah bilangan input/kode. Jika digunakan untuk membandingkan dua input dan kemudian menyatakan apakah kedua input tersebut sama, lebih besar atau lebih kecil, maka rangkaian tersebut dinamakan Magnitudo Comparator.

Tabel kebenaran

| $X_i$ | $Y_i$ | $X > Y$ | $X = Y$ | $X < Y$ |

|-------|-------|---------|---------|---------|

| 0     | 0     | 0       | 1       | 0       |

| 0     | 1     | 0       | 0       | 1       |

|   |   |   |   |   |

|---|---|---|---|---|

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

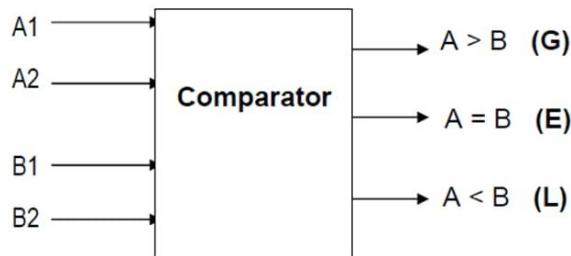

### Komparator 2 input 2 bit

| Input |    |     |    | Output |       |       |

|-------|----|-----|----|--------|-------|-------|

| (A)   |    | (B) |    | (A<B)  | (A=B) | (A>B) |

| A1    | A2 | B1  | B2 | L      | E     | G     |

| 0     | 0  | 0   | 0  | 0      | 1     | 0     |

| 0     | 0  | 0   | 1  | 1      | 0     | 0     |

| 0     | 0  | 1   | 0  | 1      | 0     | 0     |

| 0     | 0  | 1   | 1  | 1      | 0     | 0     |

| 0     | 1  | 0   | 0  | 0      | 0     | 1     |

| 0     | 1  | 0   | 1  | 0      | 1     | 0     |

| 0     | 1  | 1   | 0  | 1      | 0     | 0     |

| 1     | 0  | 0   | 0  | 0      | 0     | 1     |

| 1     | 0  | 0   | 1  | 0      | 0     | 1     |

| 1     | 0  | 1   | 0  | 0      | 1     | 0     |

| 1     | 0  | 1   | 1  | 1      | 0     | 0     |

| 1     | 1  | 0   | 0  | 0      | 0     | 1     |

| 1     | 1  | 0   | 1  | 0      | 0     | 1     |

| 1     | 1  | 1   | 0  | 0      | 0     | 1     |

| 1     | 1  | 1   | 1  | 0      | 1     | 0     |

$$L = \overline{A_1}B_1 + \overline{A_1}\overline{A_2}B_2 + \overline{A_2}B_1B_2$$

$$G = A_1\overline{B_1} + A_1A_2\overline{B_2} + A_2\overline{B_1}\overline{B_2}$$

$$E = \overline{A_1}\overline{A_2}\overline{B_1}\overline{B_2} + \overline{A_1}A_2\overline{B_1}B_2 + A_1\overline{A_2}B_1\overline{B_2} + A_1A_2B_1B_2$$

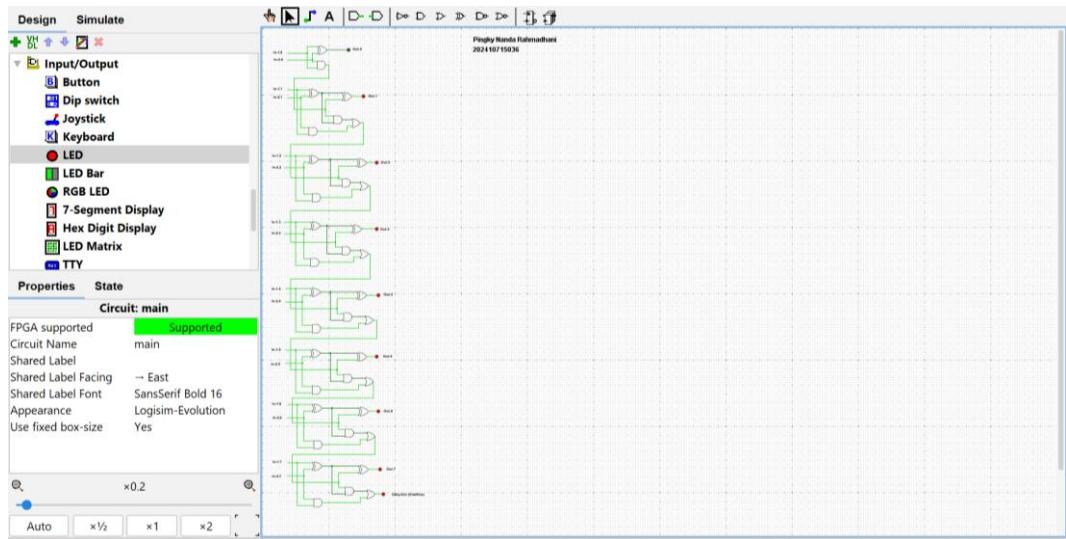

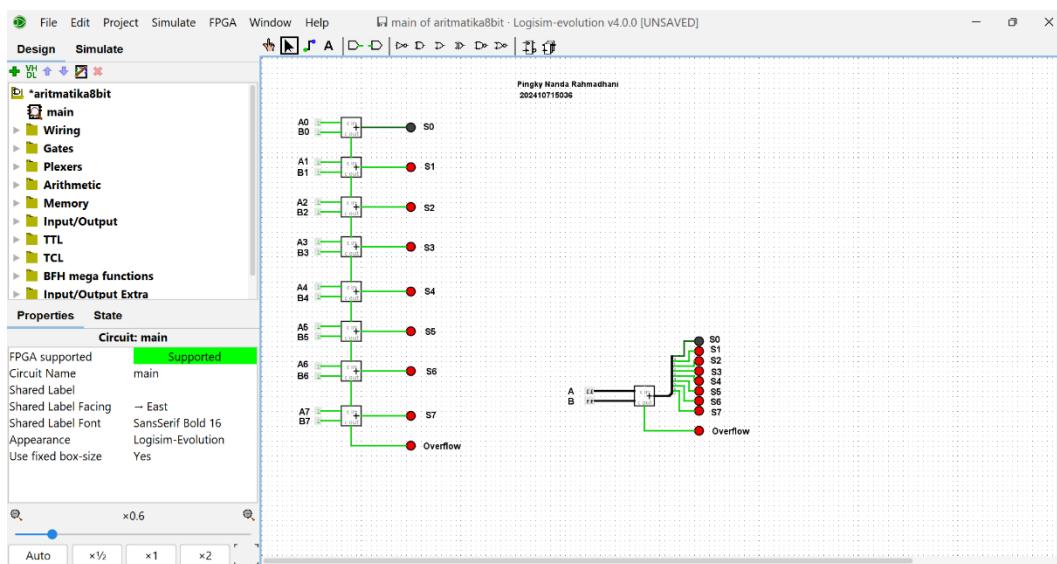

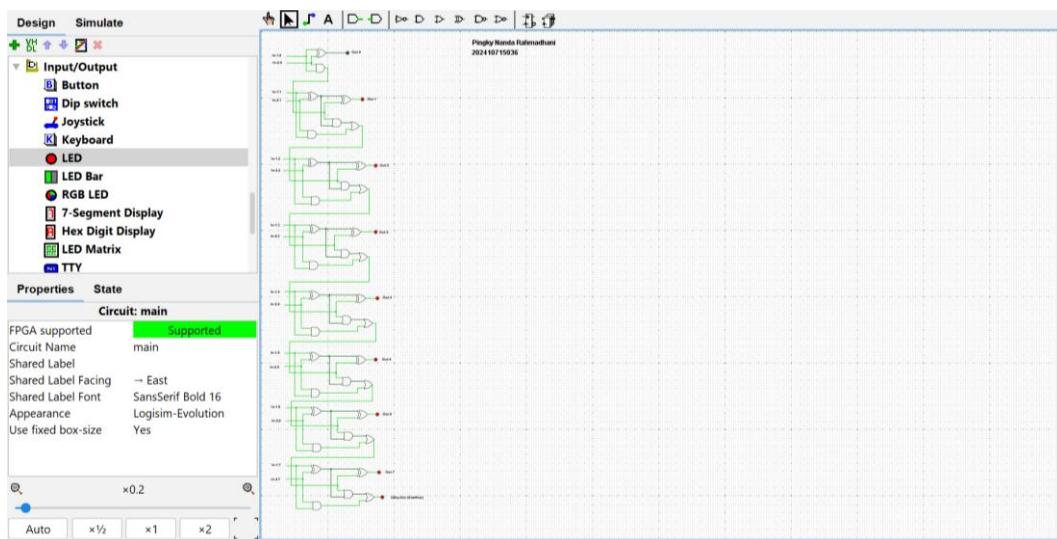

### 3) 8-bit Adder

Langkah-langkah kerja:

1. Siapkan komponen: gerbang XOR, AND, OR, switch input (constant), serta LED/probe untuk output.

2. Rancang Half Adder menggunakan satu XOR (sum) dan satu AND (carry).

3. Rancang Full Adder dengan menggabungkan dua half adder dan satu OR untuk menghasilkan carry-out.

4. Menggandakan rangkaian full adder menjadi 7 buah untuk membentuk adder bit 1 hingga bit 7.

5. Menghubungkan Carry-out setiap bit ke carry-in bit berikutnya, sehingga membentuk ripple-carry.

6. Sambungkan input A0-A7 dan B0-B7 ke blok adder yang sesuai, lalu hubungkan output S0-S7 ke LED.

7. Hubungkan carry-out dari bit 7 sebagai output carry-out atau overflow.

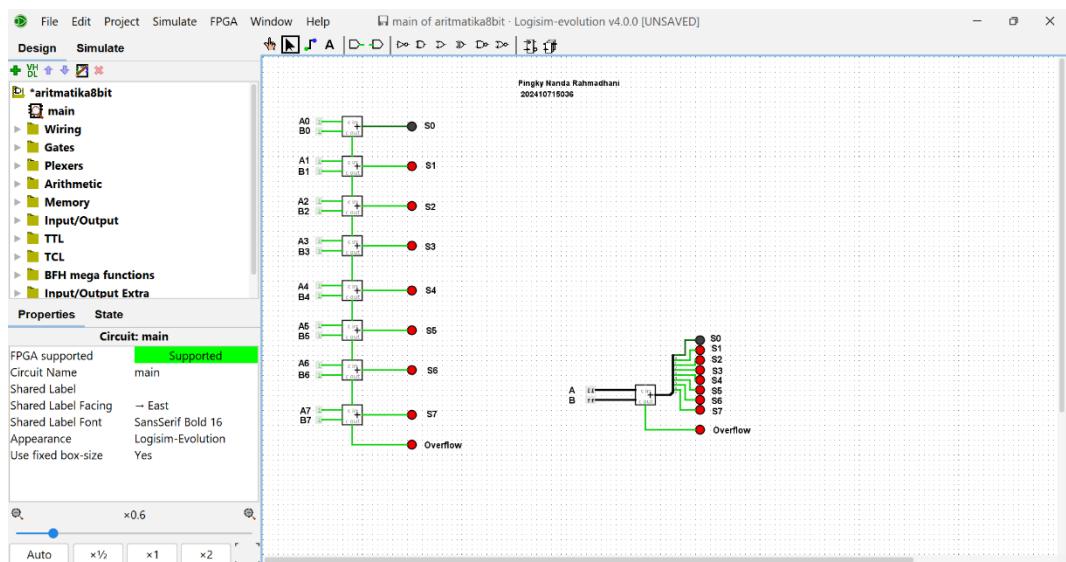

## Menggunakan Komponen Aritmatika

Langkah-langkah Kerja:

1. Masukkan delapan input A0-A7 dan B0-B7 kemudian hubungkan masing-masing pasangan bit ke komponen Adder dari menu Arithmetic.

2. Untuk tiap bit (0 sampai 7) sambungkan output S dari adder ke LED indikator S0-S7 seperti pada gambar.

3. Sambungkan ouput Cout dari adder (carry out) ke LED overflow.

4. Pastikan semua input A dan B tersambung ke adder secara pararel, dan seluruh output S0-S7 tersambung ke bar LED di sisi kanan.

5. Lakukan pengujian dengan mengubah nilai A0-A7 dan B0-B7, lalu amati LED hasil S0-S7 serta indikator Overflow.

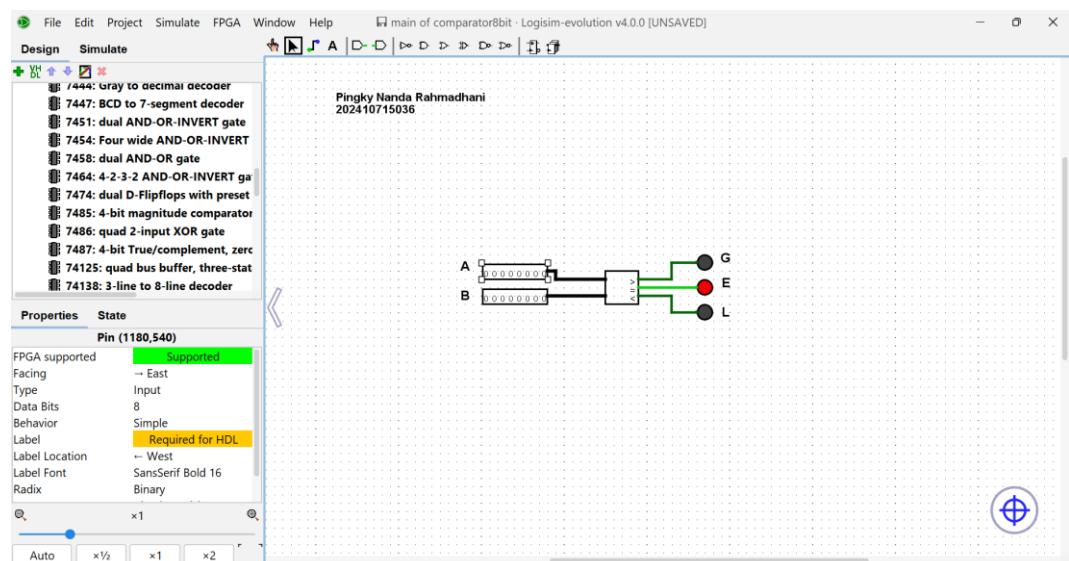

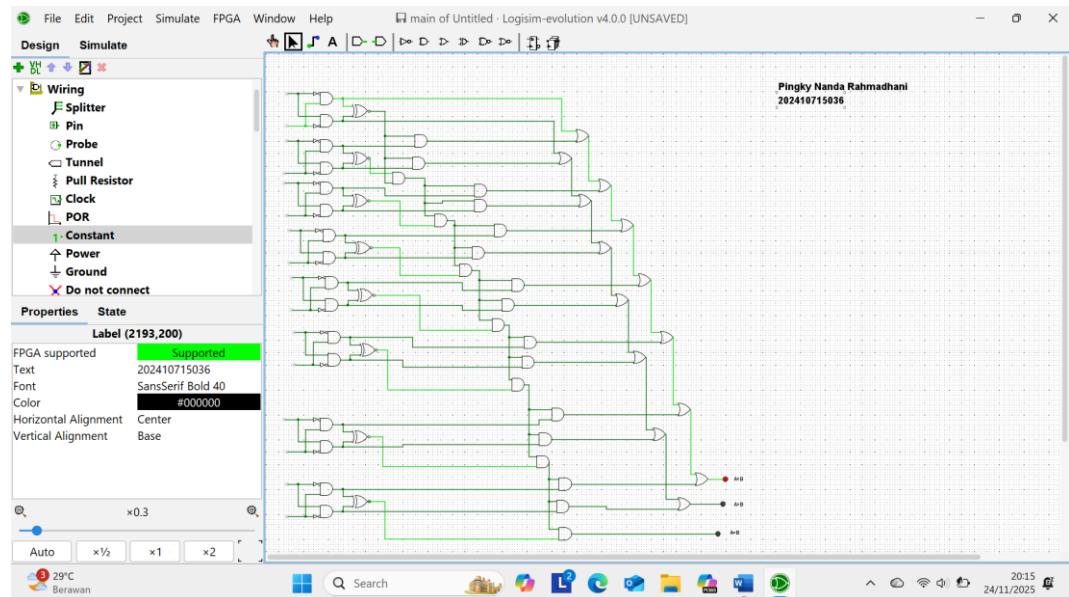

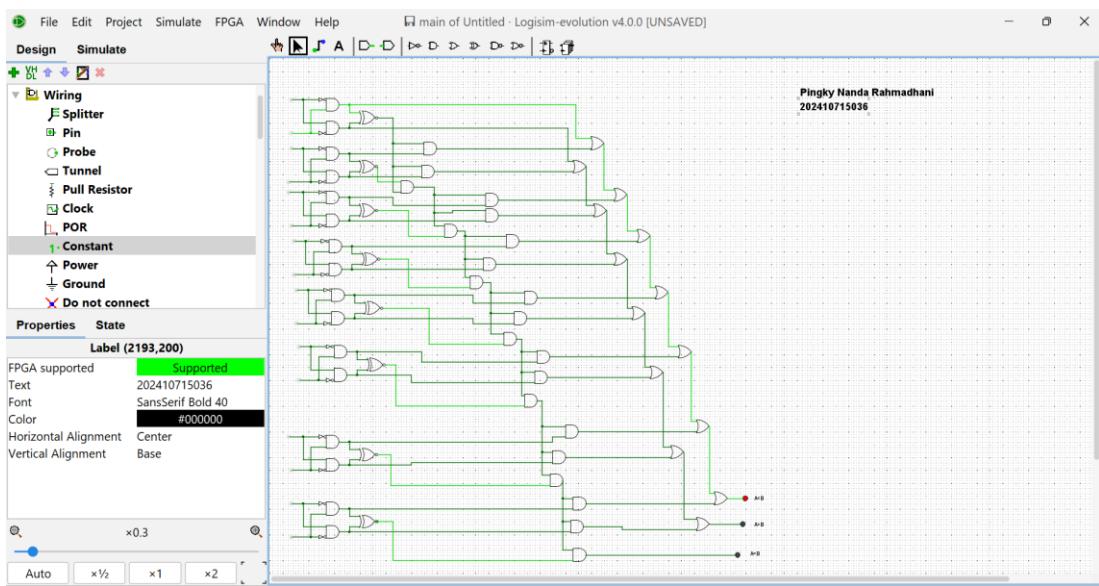

## **Comparator 8-bit**

Langkah-langkah Kerja:

1. Menyiapkan input bit A dan B (8 pasang bit)

- Rancang delapan pasang input bit yaitu A7-A0 dan B7-B0

- A7 dan B7 adalah MSB, sedangkan A0 dan B0 adalah LSB

- Setiap pasangan bit akan dibandingkan menggunakan rangkaian gerbang logika dasar (AND, OR, NOT, XOR).

2. Membangun comparator 1-bit untuk setiap pasangan Ai dan Bi

- $A_i > B_i$  menggunakan rangkaian AND dan NOT

- $A_i < B_i$  memakai kombinasi AND dan NOT

- $A_i = B_i$  menggunakan gerbang XNOR

3. Menyusun comparator secara berantai dari MSB ke LSB

4. Membuat jalur  $A > B$ ,  $A < B$ , dan  $A = B$

- Setiap tingkatan comparator dihubungkan ke jaringan OR yang mengumpulkan hasil  $A > B$  dari tiap posisi, tetapi hanya aktif jika semua bit diatasnya equal.

- Hal yang sama dilakukan untuk  $A < B$

- Untuk  $A = B$ , semua XNOR dari A7-A0 harus bernilai 1, lalu di AND menjadi satu output

5. Menghasilkan output akhir

- Diperoleh 3 output:

- $A > B$

- $A = B$

- $A < B$

## BAB II

### PEMBAHASAN

#### A. 8-bit Adder

Pada praktikum ini, dilakukan simulasi rangkaian Half Adder dan Full Adder sebagai dasar pembuatan penjumlahan 8-bit. Half Adder digunakan pada bit terendah (A0 dan B0) karena tidak memerlukan input carry-in; gerbang XOR digunakan untuk menghasilkan output penjumlahan (S0), sementara gerbang AND menghasilkan carry-out yang menjadi input carry untuk bit berikutnya. Tahap ini menjadi dasar awal penjumlahan sebelum dilanjutkan ke rangkaian penjumlahan yang lebih kompleks.

Untuk bit-bit berikutnya ( $A_1$ – $A_7$  dan  $B_1$ – $B_7$ ), digunakan Full Adder yang memiliki tiga input yaitu A, B, dan carry-in. Tujuh Full Adder disusun berantai membentuk ripple-carry adder. Setiap Full Adder menghasilkan output penjumlahan ( $S_1$ – $S_7$ ) dan carry-out yang diteruskan ke bit selanjutnya. Dalam simulasi, seluruh blok Half Adder dan Full Adder telah terhubung dengan benar, dan delapan output hasil penjumlahan ( $S_0$ – $S_7$ ) ditampilkan melalui lampu indikator. Carry-out dari bit paling signifikan digunakan sebagai indikator overflow, yang akan menyala ketika hasil penjumlahan melebihi kapasitas 8-bit. Keseluruhan rangkaian ini membuktikan bahwa kombinasi satu Half Adder dan tujuh Full Adder dapat berfungsi sebagai penjumlah 8-bit lengkap dengan kemampuan deteksi overflow.

## B. Comparator 8-bit

Pada simulasi ini dilakukan perancangan dan pengujian comparator 8-bit menggunakan Logisim, yaitu rangkaian logika yang berfungsi membandingkan dua bilangan biner masing-masing dengan panjang delapan bit. Comparator melakukan perbandingan bit per bit dimulai dari bit paling signifikan (MSB) menuju bit paling rendah (LSB). Apabila pada MSB terdapat perbedaan antara nilai A dan B, hasil perbandingan langsung ditentukan dari bit tersebut. Jika bit MSB sama, proses dilanjutkan ke bit berikutnya hingga ditemukan perbedaan atau seluruh bit bernilai sama. Dalam rancangan ini, beberapa comparator 1-bit disusun secara bertingkat (cascade), sehingga sinyal hasil perbandingan  $A > B$ ,  $A = B$ , atau  $A < B$  dari tiap bit diteruskan ke bit berikutnya sampai diperoleh keputusan akhir.

Hasil simulasi memperlihatkan bahwa rangkaian berfungsi sesuai dengan prinsip perbandingan bilangan biner. Lampu indikator  $A > B$  akan menyala jika nilai A lebih besar daripada B pada suatu bit, sedangkan indikasi  $A < B$  aktif bila A lebih kecil. Jika seluruh bit A dan B sama, lampu indikator  $A = B$  menyala. Hal ini membuktikan bahwa comparator 8-bit dapat secara akurat menentukan hubungan antara dua bilangan biner berdasarkan prioritas MSB. Dengan demikian, rangkaian comparator 8-bit yang disimulasikan berjalan dengan benar dan sesuai dengan konsep logika kombinasi pada sistem digital.

## **BAB III**

### **KESIMPULAN**

Rangkaian penjumlahan 8-bit berhasil digunakan untuk menjumlahkan dua bilangan biner 8-bit secara otomatis dengan menggabungkan satu half adder dan tujuh full adder. Penjumlahan dilakukan secara berurutan mulai dari bit paling rendah (LSB) hingga bit paling tinggi (MSB), dengan memperhitungkan sinyal carry-in dan menghasilkan carry-out yang diteruskan ke tahap berikutnya. Hasil simulasi menunjukkan bahwa rangkaian ini mampu melakukan penjumlahan bilangan biner dengan akurat, menghasilkan output jumlah 8-bit beserta carry akhir. Dengan demikian, rangkaian penjumlahah 8-bit terbukti efektif sebagai blok dasar dalam operasi aritmatika digital.

Rangkaian pembanding (comparator) 8-bit yang dirancang dapat membandingkan dua input biner 8-bit dan menentukan hubungan antara keduanya, yaitu apakah A lebih besar dari B, A sama dengan B, atau A lebih kecil dari B. Proses perbandingan dilakukan secara berurutan mulai dari bit paling signifikan (MSB) hingga bit paling rendah (LSB), sehingga keputusan akhir dipengaruhi oleh perbedaan pada bit dengan bobot tertinggi. Hasil simulasi membuktikan bahwa rangkaian ini memberikan keluaran indikator yang tepat melalui tiga sinyal output:  $A > B$ ,  $A = B$ , dan  $A < B$ . Oleh karena itu, comparator 8-bit ini bekerja secara akurat sebagai rangkaian logika untuk pembandingan digital.