## **LAPORAN PRAKTIKUM PENGANTAR SISTEM DIGITAL**

**Dosen: Arif Rifai Dwiyanto, ST., MTI**

### **RANGKAIAN KOMBINASI-HALF ADDER DAN FULL ADDER**

**Disusun Oleh:**

**Khoirunnisa**

**(202410715047)**

**F3A6**

**PROGRAM STUDI INFORMATIKA FAKULTAS ILMU KOMPUTER**

**UNIVERSITAS BHAYANGKARA JAKARTA RAYA**

**2025**

# BAB I

## PENDAHULUAN

### 1.1 Tujuan

1. Mahasiswa memahami konsep rangkaian kombinasi

2. Mahasiswa mampu membangun rangkaian Half Adder dan Full Adder menggunakan logism

### 1.2 Alat dan Bahan:

1. Laptop/PC dengan aplikasi Logisim Evolution terinstal

2. Modul panduan praktikum

3. Buku catatan

### 1.3 Langkah-langkah Kerja

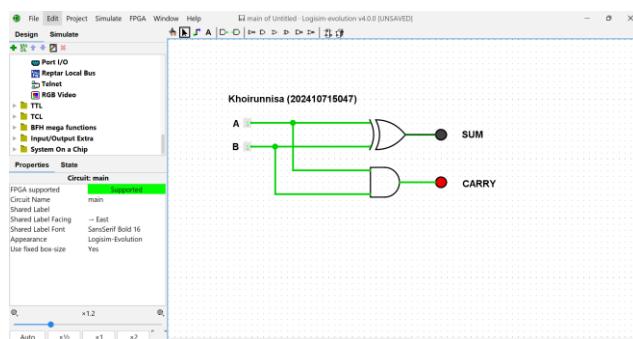

#### 1.2.1 Membuat Half Adder

- 1) **Langkah 1:** bangun rangkaian Half Adder dengan Ekspresi logika berikut:

- $S = A \oplus B \text{ (XOR)}$

- $C = A \cdot B \text{ (AND)}$

- 2) **Langkah 2:** hubungkan input A dan B menggunakan Constant

- 3) **Langkah 3:** tambahkan LED pada output S (sum) dan C (carry)

| A | B | Sum (S) | Carry (C) |

|---|---|---------|-----------|

| 0 | 0 | 0       | 0         |

| 0 | 1 | 1       | 0         |

| 1 | 0 | 1       | 0         |

| 1 | 1 | 0       | 1         |

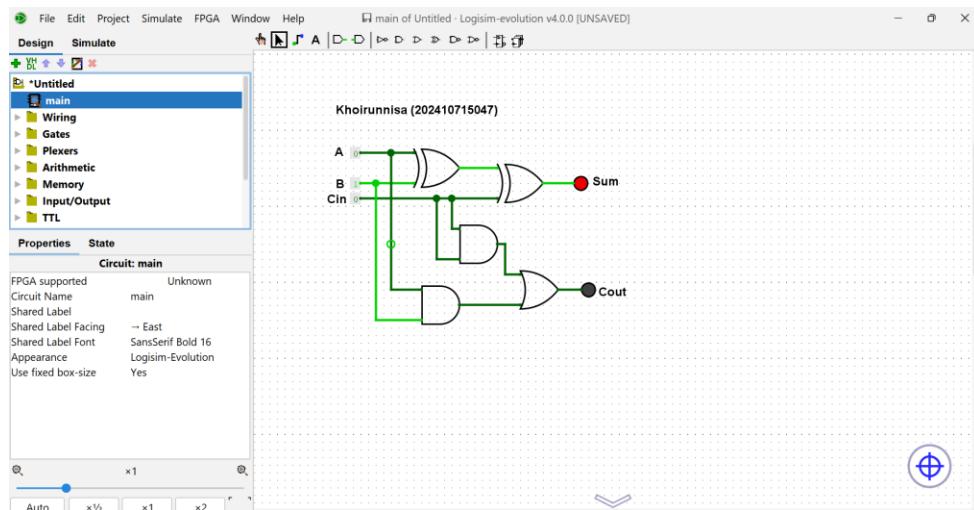

#### 1.2.2 Mmembuat Full Adder

1) **Langkah 1:** angun rangkaian Full Adder dengan Ekspresi logika berikut:

- $S = (A \oplus B) \oplus C_{in}$

- $C_{out} = (A \cdot B) + ((A \oplus B) \cdot C_{in})$

- 2) **Langkah 2:** Gunakan dua gerbang XOR, dua gerbang AND, dan satu gerbang OR untuk membangun rangkaian.

- 3) **Langkah 3:** Hubungkan input A, B, dan Cin menggunakan **Constant**.

- 4) **Langkah 4:** Tambahkan **LED** pada output S (sum) dan C<sub>out</sub> (carry out)

| A | B | Cin | Sum | Cout |

|---|---|-----|-----|------|

| 0 | 0 | 0   | 0   | 0    |

| 0 | 0 | 1   | 1   | 0    |

| 0 | 1 | 0   | 1   | 0    |

| 0 | 1 | 1   | 0   | 1    |

| 1 | 0 | 0   | 1   | 0    |

| 1 | 0 | 1   | 0   | 1    |

| 1 | 1 | 0   | 0   | 1    |

| 1 | 1 | 1   | 1   | 1    |

## BAB II

### HASIL SIMULASI

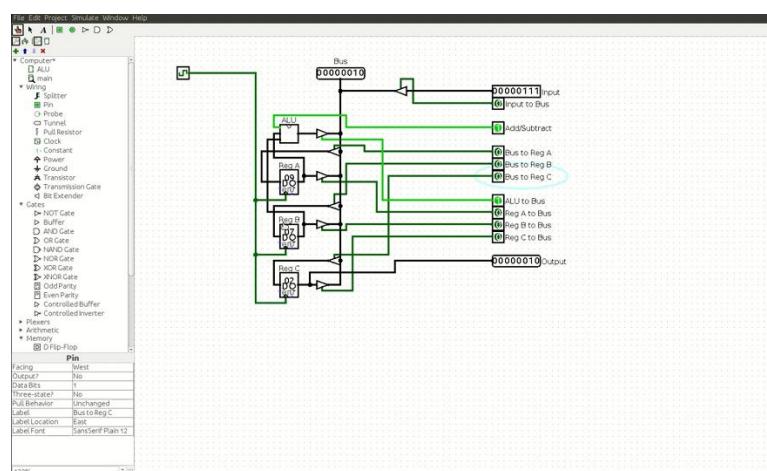

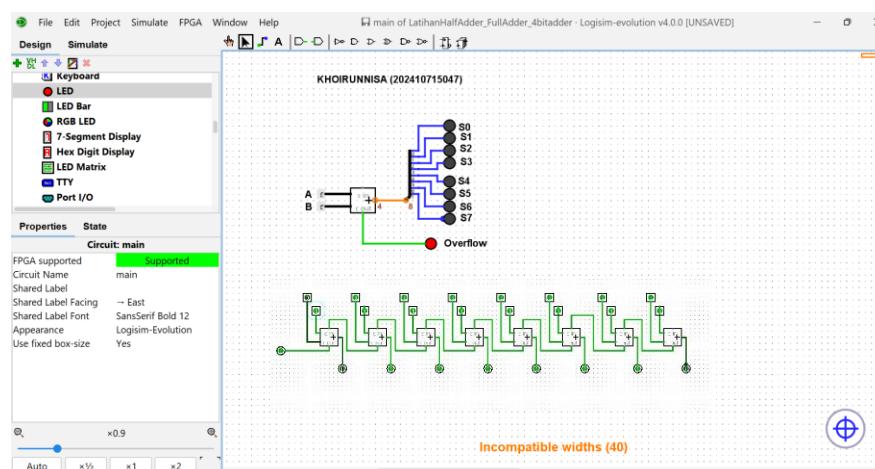

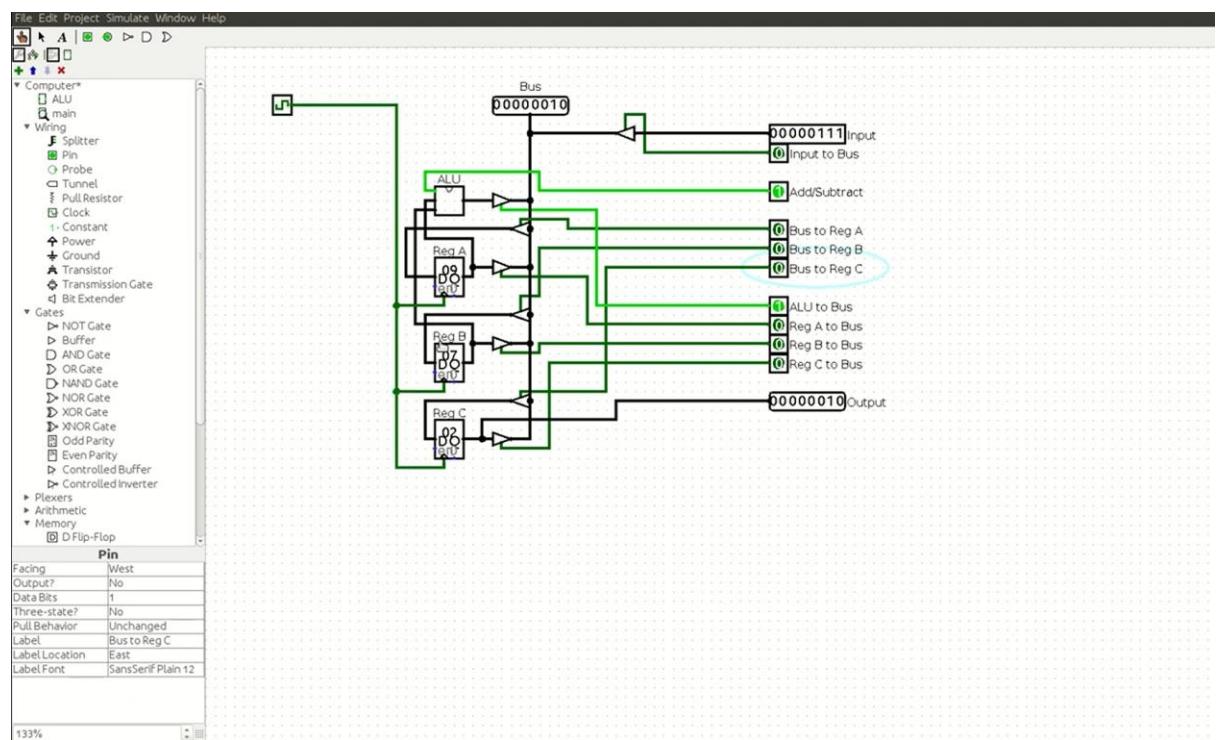

#### 2.1 8-bit adder

Menggunakan Komponen Aritmatika

## 2.2 Rangkaian Komparator

Sebuah rangkaian Comparator berfungsi membandingkan dua buah bilangan input / kode Jika digunakan untuk membandingkan dua input dan kemudian menyatakan apakah kedua input tersebut sama, lebih besar atau lebih kecil, maka rangkaian tersebut dinamakan Magnitude Comparator

| A  | B  | A>B | A=B | A<B |

|----|----|-----|-----|-----|

| 00 | 00 | 0   | 1   | 0   |

| 00 | 01 | 0   | 0   | 1   |

| 00 | 10 | 0   | 0   | 1   |

| 00 | 11 | 0   | 0   | 1   |

| 01 | 00 | 1   | 0   | 0   |

| 01 | 01 | 0   | 1   | 0   |

| 01 | 10 | 0   | 0   | 1   |

| 01 | 11 | 0   | 0   | 1   |

|    |    |   |   |   |

|----|----|---|---|---|

| 10 | 00 | 1 | 0 | 0 |

| 10 | 01 | 1 | 0 | 0 |

| 10 | 10 | 0 | 1 | 0 |

| 10 | 11 | 0 | 0 | 1 |

| 11 | 00 | 1 | 0 | 0 |

| 11 | 01 | 1 | 0 | 0 |

| 11 | 10 | 1 | 0 | 0 |

| LZ | 11 | 0 | 1 | 0 |

Set A = 00000001, B = 00000001 → SUM = 00000010, Carry = 0, Comparator: A=B = 1. Set A = 11111111 (255), B = 00000001 (1) → SM = 00000000 (overflow), Carry = 1, Comparator: A>B = 1. Set A = 00001010 (10), B = 00001111 (15) → SUM = 00011001, Carry = 0, Comparator: A<B = 1.

## BAB III

### KESIMPULAN

Berdasarkan hasil praktikum mengenai perancangan dan analisis rangkaian *Half Adder*, *Full Adder*, dan *Comparator*, dapat disimpulkan bahwa rangkaian aritmetika dan logika merupakan dasar penting dalam sistem digital. Half Adder mampu melakukan penjumlahan dua bit sederhana dan menghasilkan keluaran berupa *Sum* dan *Carry*, namun tidak dapat mengolah *carry input*. Keterbatasan ini ditingkatkan pada Full Adder yang mampu menjumlahkan tiga bit sekaligus (A, B, dan Cin), sehingga memungkinkan penyusunan rangkaian penjumlahan berskala lebih besar seperti 4-bit atau 8-bit adder menggunakan metode *ripple carry*.

Selain itu, rangkaian Comparator berfungsi untuk membandingkan dua bilangan biner dan menghasilkan tiga kondisi keluaran, yaitu A lebih besar dari B, A sama dengan B, atau A lebih kecil dari B. Melalui implementasi ketiga rangkaian tersebut pada perangkat lunak Logisim, praktikan dapat memahami hubungan antara teori gerbang logika dengan implementasinya dalam rangkaian digital. Secara keseluruhan, praktikum ini menunjukkan bahwa Half Adder, Full Adder, dan Comparator merupakan blok bangunan fundamental dalam perancangan sistem aritmetika komputasi seperti ALU dan berbagai modul pemrosesan data lainnya.