## **LAPORAN PRAKTIKUM PENGANTAR SISTEM DIGITAL**

**Dosen: Arif Rifai Dwiyanto, ST., MTI**

### **RANGKAIAN SEKUENSIAL (FLIP-FLOP)**

**Disusun Oleh:**

**Khoirunnisa**

**(202410715047)**

**F3A6**

**PROGRAM STUDI INFORMATIKA FAKULTAS ILMU KOMPUTER**

**UNIVERSITAS BHAYANGKARA JAKARTA RAYA**

**2025**

## BAB I

### PENDAHULUAN

#### 1.1 Tujuan

1. Mahasiswa memahami konsep rangkaian sequential

2. Mahasiswa mampu merancang dan mensimulasikan flip-flop dasar (SR, D, dan JK)

#### 1.2 Alat dan Bahan:

1. Laptop/PC dengan aplikasi Logisim Evolution terinstal

2. Modul panduan praktikum

3. Buku catatan

4. Komponen logika: gerbang NOR, NAND, NOT, AND, XOR

5. LED sebagai indicator jumper

#### 1.3 Langkah-langkah Kerja:

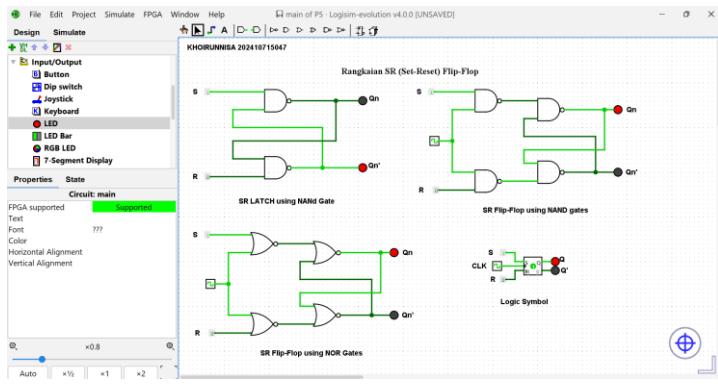

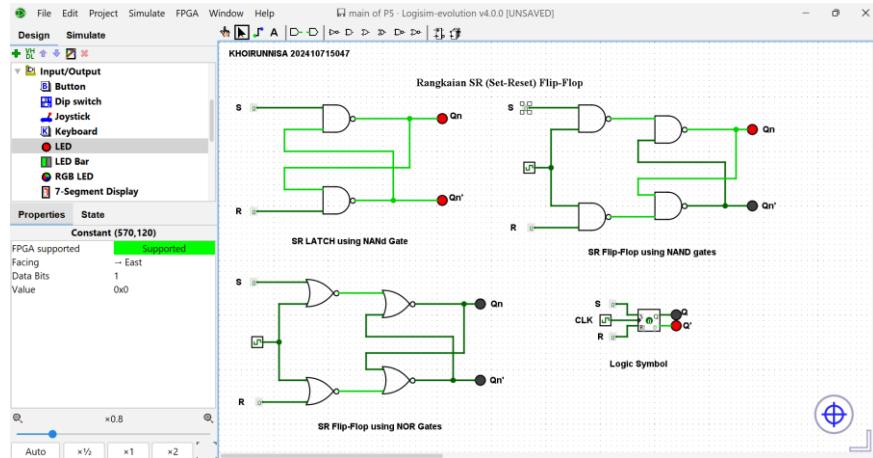

##### 1.4.1 Membuat Rangkaian SR (Set-Reset) Flip-Flop

1. Bangun rangkaian SR Flip-flop menggunakan dua gerbang NOR atau NAND:

- Output dari masing-masing gerbang diumpan balik ke input gerbang satunya.

- Pin S masuk ke gerbang NOR/NAND kiri, R ke gerbang kanan.

2. Hubungkan LED pada keluaran Q dan Q'

3. Uji kombinasi input S dan R:

- 0 0 → No Change

- 0 1 → Reset

- 1 0 → Set

- 1 1 → Invalid (NOR) / No Change (NAND)

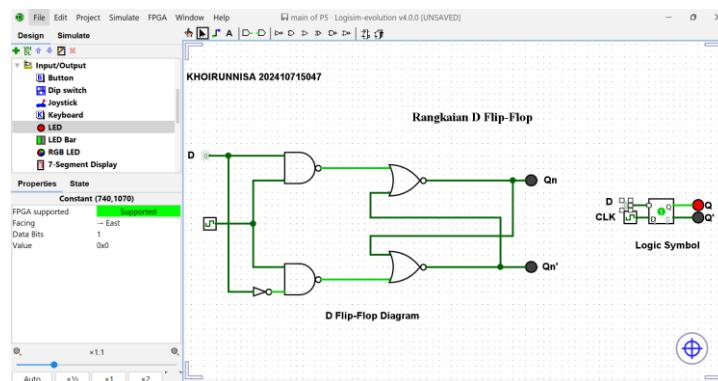

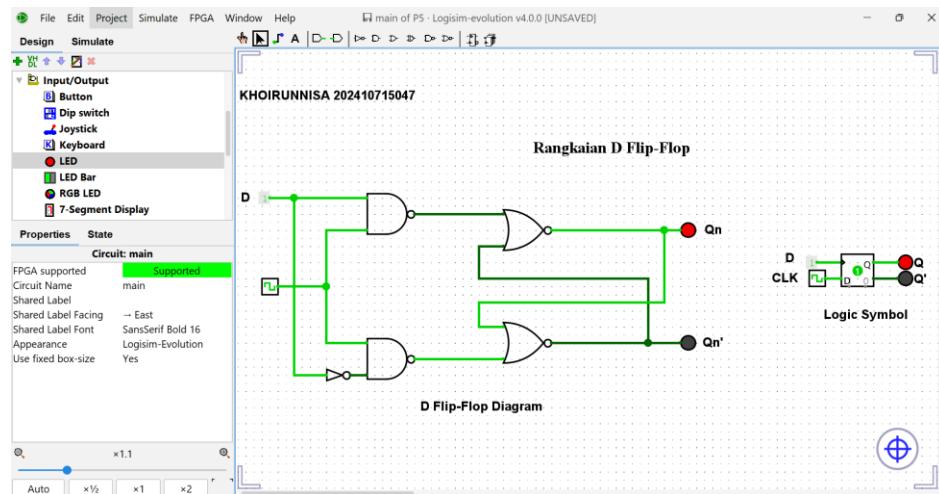

### 1.4.2 Membuat Rangkaian D Flip-Flop

1. Tambah gerbang NOT pada input D:

- $D \rightarrow S$

- $\text{NOT}(D) \rightarrow R$

2. Rangkaian SR sekarang menjadi D Flip-flop

3. Simulasikan rangkaian:

- $D = 0 \rightarrow Q(\text{next})=0$

- $D = 1 \rightarrow Q(\text{next})=1$

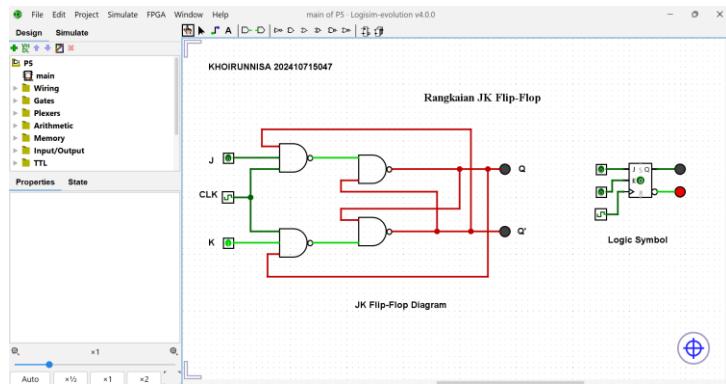

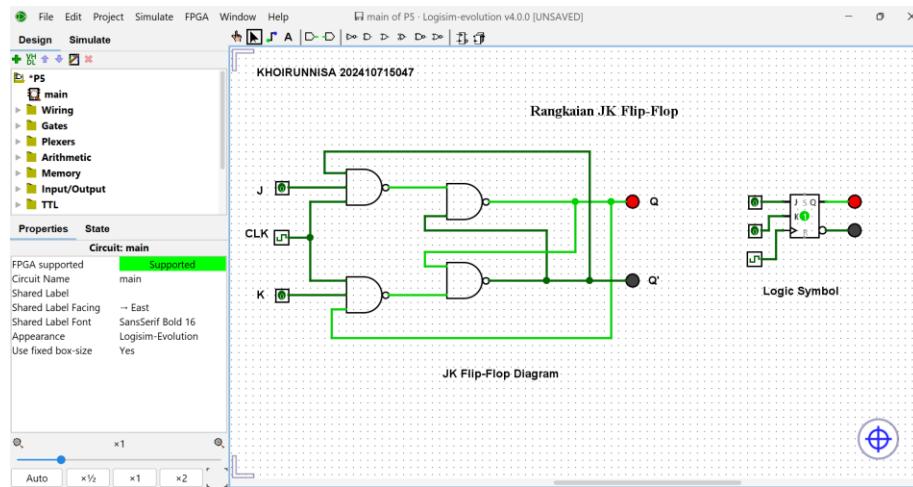

### 1.4.3 Membuat Rangkaian JK Flip-Flop

1. Bangun rangkaian SR Flip-flop sebagai dasar.

2. Tambahkan rangkaian logika pengendali untuk input J dan K:

- J diketahui AND dengan  $Q'$  sebelum masuk ke S

- K diketahui AND dengan Q sebelum masuk ke R

Sehingga:

- $S = J \cdot Q'$

- $R = K \cdot Q$

3. Hubungkan clock bila diperlukan (jika JK yang digunakan Adalah edge-triggered).

4. Uji fungsi:

- $J=0, K=0 \rightarrow \text{No Change}$

- $J=0, K=1 \rightarrow \text{Reset}$

- $J=1, K=0 \rightarrow \text{Set}$

- $J=1, K=1 \rightarrow \text{Toggle}$

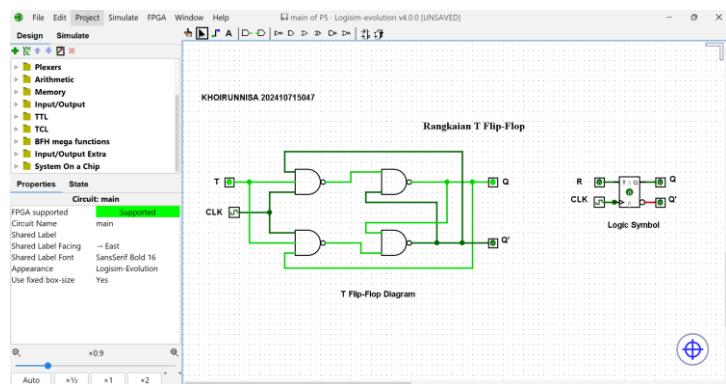

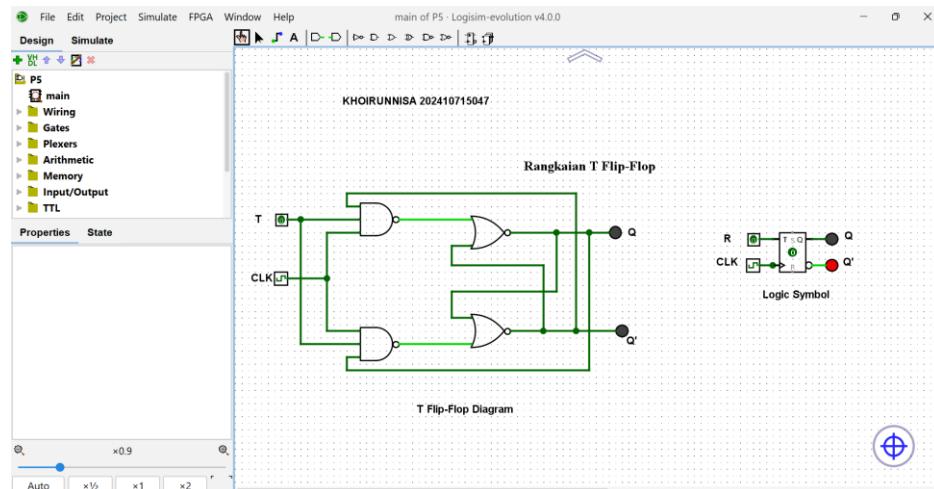

#### 1.4.4 Membuat Rangkaian T (Toggle) Flip-Flop

1. Siapkan satu JK Flip-flop sebagai dasar.

2. Hubungkan input T ke kedua input JK:

- $J = T$

- $K = T$

3. Hasilnya:

- Jika  $T = 0 \rightarrow \text{No Change}$

- Jika  $T = 1 \rightarrow \text{Toggle} (Q(\text{next}) = \neg Q)$

4. Uji rangkaian pada simulator untuk memastikan Q berubah ketika  $T=1$

## BAB II

### HASIL SIMULASI

#### 3.1 Hasil Implementasi Rangkaian SR (Set-Reset) Flip-Flop

| Trigger | Inputs |   | Output        |            |   |    | State         |

|---------|--------|---|---------------|------------|---|----|---------------|

|         |        |   | Present State | Next State | Q | Q' |               |

| CLK     | S      | R | Q             | Q'         | Q | Q' |               |

| Π       | X      | X | -             |            | - |    | No Change     |

| Π       | 0      | 0 | 0             | 1          | 0 | 1  | No Change     |

|         |        |   | 1             | 0          | 1 | 0  |               |

| Π       | 0      | 1 | 0             | 1          | 0 | 1  | Reset         |

|         |        |   | 1             | 0          | 0 | 1  |               |

| Π       | 1      | 0 | 0             | 1          | 1 | 0  | Set           |

|         |        |   | 1             | 0          | 1 | 0  |               |

| Π       | 1      | 1 | 0             | 1          | - | -  | Indeterminate |

|         |        |   | 1             | 0          | - | -  |               |

Berdasarkan tabel kebenaran di atas, dapat diketahui bahwa rangkaian SR Flip-Flop bekerja sesuai dengan prinsip dasarnya. Pada saat  $S = 0$  dan  $R = 0$ , keluaran  $Q$  dan  $Q'$  mempertahankan keadaan sebelumnya (no change). Ketika  $S = 0$  dan  $R = 1$ , rangkaian berada pada kondisi reset dengan keluaran  $Q = 0$  dan  $Q' = 1$ , sedangkan pada kondisi  $S = 1$  dan  $R = 0$ , rangkaian berada pada kondisi set dengan keluaran  $Q = 1$  dan  $Q' = 0$ . Namun, pada kondisi  $S = 1$  dan  $R = 1$ , keluaran menjadi tidak terdefinisi (indeterminate) karena kedua input aktif secara bersamaan.

### 3.2 Hasil Implementasi Rangkaian D Flip-Flop

| Trigger | Inputs | Output        |    |            |    | State     |

|---------|--------|---------------|----|------------|----|-----------|

|         |        | Present State |    | Next State |    |           |

| CLK     | D      | Q             | Q' | Q          | Q' |           |

|         | 0      | 1             | 1  | 0          | 1  | No Change |

| Π       | 0      | 1             | 1  | 1          | 0  | Reset     |

|         | 1      | 1             | 1  | 0          | 1  | No Change |

| Π       | 1      | 0             | 0  | 0          | 1  | Set       |

Berdasarkan tabel kebenaran di atas, dapat diketahui bahwa rangkaian D Flip-Flop bekerja sesuai dengan karakteristiknya. Pada saat clock aktif ( $\Pi$ ), nilai keluaran Q akan mengikuti nilai input D. Ketika D = 0, keluaran berada pada kondisi reset dengan  $Q = 0$  dan  $Q' = 1$ , sedangkan saat D = 1, rangkaian berada pada kondisi set dengan  $Q = 1$  dan  $Q' = 0$ . Jika tidak terjadi perubahan pada sinyal clock, maka keluaran Q dan Q' akan mempertahankan keadaan sebelumnya (no change). Hal ini menunjukkan bahwa D Flip-Flop mampu menyimpan data dengan baik dan hanya berubah sesuai input pada saat trigger clock aktif.

### 3.3 Hasil Implementasi Rangkaian JK Flip-Flop

| Trigger | Inputs |   | Output        |    |            |    | State         |

|---------|--------|---|---------------|----|------------|----|---------------|

|         |        |   | Present State |    | Next State |    |               |

| CLK     | J      | K | Q             | Q' | Q          | Q' |               |

| Π       | X      | X | -             | -  | -          | -  | Latched       |

| Π       | 0      | 0 | 0             | 1  | 0          | 1  | No Change     |

|         |        |   | 1             | 0  | 1          | 0  |               |

| Π       | 0      | 1 | 0             | 1  | 0          | 1  | Reset         |

|         |        |   | 1             | 0  | 0          | 1  |               |

| Π       | 1      | 0 | 0             | 1  | 1          | 0  | Set           |

|         |        |   | 1             | 0  | 1          | 0  |               |

| Π       | 1      | 1 | 0             | 1  | 1          | 0  | Indeterminate |

|         |        |   | 1             | 0  | 0          | 1  |               |

Berdasarkan tabel kebenaran di atas, dapat diketahui bahwa rangkaian JK Flip-Flop bekerja sesuai dengan karakteristiknya. Saat  $J = 0$  dan  $K = 0$ , keluaran  $Q$  dan  $Q'$  mempertahankan keadaan sebelumnya (no change). Pada kondisi  $J = 0$  dan  $K = 1$ , rangkaian berada pada keadaan reset dengan  $Q = 0$  dan  $Q' = 1$ , sedangkan pada kondisi  $J = 1$  dan  $K = 0$ , rangkaian berada pada keadaan set dengan  $Q = 1$  dan  $Q' = 0$ . Ketika  $J = 1$  dan  $K = 1$ , keluaran mengalami perubahan secara bergantian (toggle) sesuai dengan keadaan sebelumnya. Hal ini menunjukkan bahwa JK Flip-Flop mampu mengatasi kondisi terlarang pada SR Flip-Flop dan bekerja secara stabil sesuai input dan sinyal clock.

### 3.4 Hasil Implementasi Rangkaian T Flip-Flop

| <b>CLK</b> | <b>T</b> | <b>Q<sub>n</sub></b> | <b>Q<sub>n+1</sub></b> | <b>Ket</b>         |

|------------|----------|----------------------|------------------------|--------------------|

| Π          | 0        | 0                    | 0                      | Hold/tidak berubah |

| Π          | 0        | 1                    | 1                      | Hold/tidak berubah |

| Π          | 1        | 0                    | 1                      | Toggle/ubah ke 1   |

| Π          | 1        | 1                    | 0                      | Toggle/ubah ke 0   |

Berdasarkan tabel kebenaran di atas, dapat diketahui bahwa rangkaian T Flip-Flop bekerja sesuai dengan prinsip dasarnya. Pada saat  $T = 0$ , keluaran Q mempertahankan keadaan sebelumnya (hold/tidak berubah) meskipun sinyal clock aktif. Sementara itu, ketika  $T = 1$ , keluaran Q akan mengalami perubahan (toggle), yaitu berpindah dari 0 ke 1 atau dari 1 ke 0 sesuai dengan nilai sebelumnya. Hasil ini menunjukkan bahwa T Flip-Flop berfungsi sebagai pencacah (toggle flip-flop) dan hanya mengubah keadaan keluaran saat input T bernilai aktif.

## BAB III

### KESIMPULAN

Berdasarkan hasil praktikum yang telah dilakukan, dapat disimpulkan bahwa flip-flop sekuensial merupakan komponen dasar dalam elektronika digital yang berfungsi sebagai penyimpan data biner (0 dan 1). Flip-flop termasuk ke dalam rangkaian sekuensial, di mana nilai keluarannya bergantung pada input saat ini, kondisi sebelumnya, serta dikendalikan oleh sinyal clock. Flip-flop memiliki dua keluaran stabil, yaitu Q dan Q', yang nilainya saling berlawanan.

Dari hasil simulasi, SR Flip-Flop menunjukkan kemampuan dasar dalam menyimpan data, dengan kondisi set, reset, no change, serta satu kondisi terlarang saat kedua input aktif bersamaan. D Flip-Flop bekerja dengan menyalin nilai input D ke keluaran Q pada saat clock aktif, sehingga lebih stabil dan banyak digunakan sebagai elemen penyimpanan data. JK Flip-Flop merupakan pengembangan dari SR Flip-Flop yang mampu menghilangkan kondisi terlarang, di mana saat  $J = K = 1$  keluaran akan mengalami perubahan secara bergantian (toggle). Sementara itu, T Flip-Flop berfungsi sebagai flip-flop pencacah, di mana keluaran akan tetap ketika  $T = 0$  dan berubah (toggle) saat  $T = 1$ .

Dengan demikian, hasil simulasi membuktikan bahwa setiap jenis flip-flop memiliki karakteristik dan fungsi yang berbeda, namun saling melengkapi dalam membangun rangkaian digital yang lebih kompleks seperti counter, register, dan sistem memori.