**LAPORAN PRAKTIKUM PENGANTAR SISTEM DIGITAL**

**MULTIPLEXER DAN DEMULTIPLEXER**

**Dosen: Arif Rifa'i Dwiyanto, ST., MTI**

**Hanif Fauziyyah (202410715172)**

**F3A6**

**PROGRAM STUDI INFORMATIKA – FAKULTAS ILMU

KOMPUTER

UNIVERSITAS BHAYANGKARA JAKARTA RAYA

2025**

# BAB I

## PENDAHULUAN

### 1.1 Tujuan

- A. Mahasiswa memahami konsep kerja Multiplexer (MUX) dan Demultiplexer (DEMUX).

- B. Mahasiswa mampu merancang dan mensimulasikan MUX dan DEMUX menggunakan Logisim.

### 1.2 Langkah-Langkah Kerja

#### A. Merancang 8-to-1 Multiplexer

- Tambahkan 8 Constant untuk input  $I_0, I_1, I_2, I_3, I_4, I_5, I_6, I_7$ .

- Tambahkan 3 Constant untuk select lines  $S_0, S_1$ , dan  $S_2$ .

- Gunakan kombinasi gerbang AND, OR, dan NOT sesuai ekspresi logika.

- Tambahkan LED untuk melihat hasil output  $Y$ .

- Simulasikan rangkaian dengan berbagai kombinasi input dan select lines.

- Input :  $I_0, I_1, I_2, I_3, I_4, I_5, I_6, I_7$

- Select Lines :  $S_0, S_1, S_2$

- Output :  $Y$

- Ekspresi Logika Output :

$$Y = (S0'.S1'.S2'.I_0) + (S0'.S1'.S2.I_1) + (S0'.S1.S2'.I_2) + \\ (S0'.S1.S2.I_3) + (S0.S1'.S2'.I_4) + (S0.S1'.S2.I_5) + (S0.S1.S2'.I_6) + \\ (S0.S1.S2.I_7)$$

- Tabel kebenaran :

| S0 | S1 | S2 | Y              |

|----|----|----|----------------|

| 0  | 0  | 0  | I <sub>0</sub> |

| 0  | 0  | 1  | I <sub>1</sub> |

| 0  | 1  | 0  | I <sub>2</sub> |

| 0  | 1  | 1  | I <sub>3</sub> |

| 1  | 0  | 0  | I <sub>4</sub> |

| 1  | 0  | 1  | I <sub>5</sub> |

| 1  | 1  | 0  | I <sub>6</sub> |

| 1  | 1  | 1  | I <sub>7</sub> |

## B. Merancang 1-to-8 Demultiplexer

- Tambahkan 1 Constant untuk input I.

- Tambahkan 3 Constant untuk select lines S0, S1, dan S2.

- Gunakan kombinasi gerbang AND dan NOT sesuai ekspresi logika untuk setiap output.

- Hubungkan setiap output ke LED.

- Simulasikan rangkaian dengan berbagai kombinasi select lines dan input I

- Input : I

- Select Lines : S0, S1, S2

- Output : Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7

- Ekspresi Logika Output :

$$Y_0 = S_0' \cdot S_1' \cdot S_2' \cdot I$$

$$Y_1 = S_0' \cdot S_1' \cdot S_2 \cdot I$$

$$Y_2 = S_0' \cdot S_1 \cdot S_2' \cdot I$$

$$Y_3 = S_0' \cdot S_1 \cdot S_2 \cdot I$$

$$Y_4 = S_0 \cdot S_1' \cdot S_2' \cdot I$$

$$Y_5 = S_0 \cdot S_1' \cdot S_2 \cdot I$$

$$Y_6 = S_0 \cdot S_1 \cdot S_2' \cdot I$$

$$Y_7 = S_0 \cdot S_1 \cdot S_2 \cdot I$$

- Tabel Kebenaran :

| Selection Lines |    |    | Output |    |    |    |    |    |    |    |

|-----------------|----|----|--------|----|----|----|----|----|----|----|

| S0              | S1 | S2 | Y0     | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

| 0               | 0  | 0  | 1      | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0               | 0  | 1  | 0      | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0               | 1  | 0  | 0      | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 0               | 1  | 1  | 0      | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| 1               | 0  | 0  | 0      | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

|   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

## BAB II

### PEMBAHASAN

Pada praktikum ini, mahasiswa melakukan perancangan dan simulasi rangkaian Multiplexer (MUX) 8-to-1 serta Demultiplexer (DEMUX) 1-to-8 menggunakan perangkat lunak Logisim. Pembahasan mencakup cara kerja rangkaian, penerapan ekspresi logika, serta hasil yang tampak dari proses simulasi.

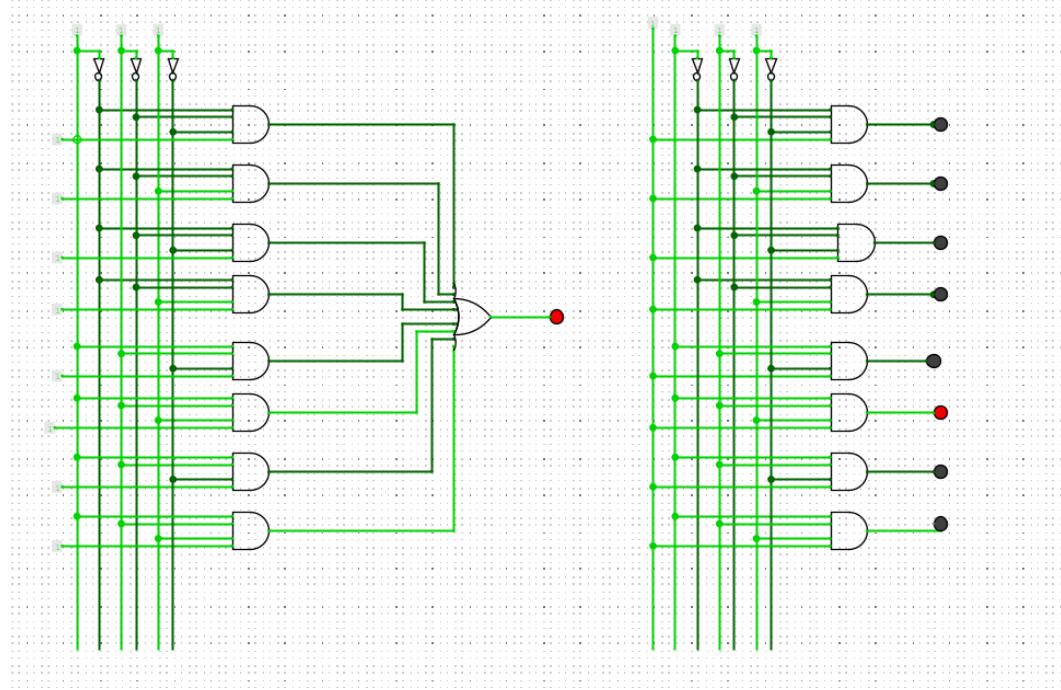

#### 1. Pembahasan Multiplexer 8-to-1

Multiplexer bekerja dengan memilih satu dari delapan input ( $I_0$ – $I_7$ ) berdasarkan kombinasi tiga bit select line ( $S_0$ ,  $S_1$ ,  $S_2$ ). Setiap kombinasi select line menentukan input mana yang diteruskan ke output Y.

Dalam implementasinya, rangkaian dibuat menggunakan gerbang AND, OR, dan NOT untuk mewujudkan ekspresi logika:

$$Y = (S_0 S_1 S_2 I_0) + (S_0 S_1 S_2 I_1) + (S_0 S_1 S_2 I_2) + (S_0 S_1 S_2 I_3) + (S_0 S_1 S_2 I_4) + (S_0 S_1 S_2 I_5) + (S_0 S_1 S_2 I_6) + (S_0 S_1 S_2 I_7)$$

Setiap suku menggunakan kombinasi gerbang AND untuk mencocokkan pola  $S_0$ ,  $S_1$ ,  $S_2$  tertentu dan mengalikan input yang sesuai. Selanjutnya semua suku dijumlahkan dengan gerbang OR sehingga menghasilkan satu output Y.

Dari hasil simulasi, rangkaian bekerja sesuai tabel kebenaran, di mana setiap kali select line berubah, output Y mengikuti input yang sesuai. Hal ini menunjukkan bahwa logika rangkaian telah dirancang dengan benar dan MUX dapat memilih data secara tepat.

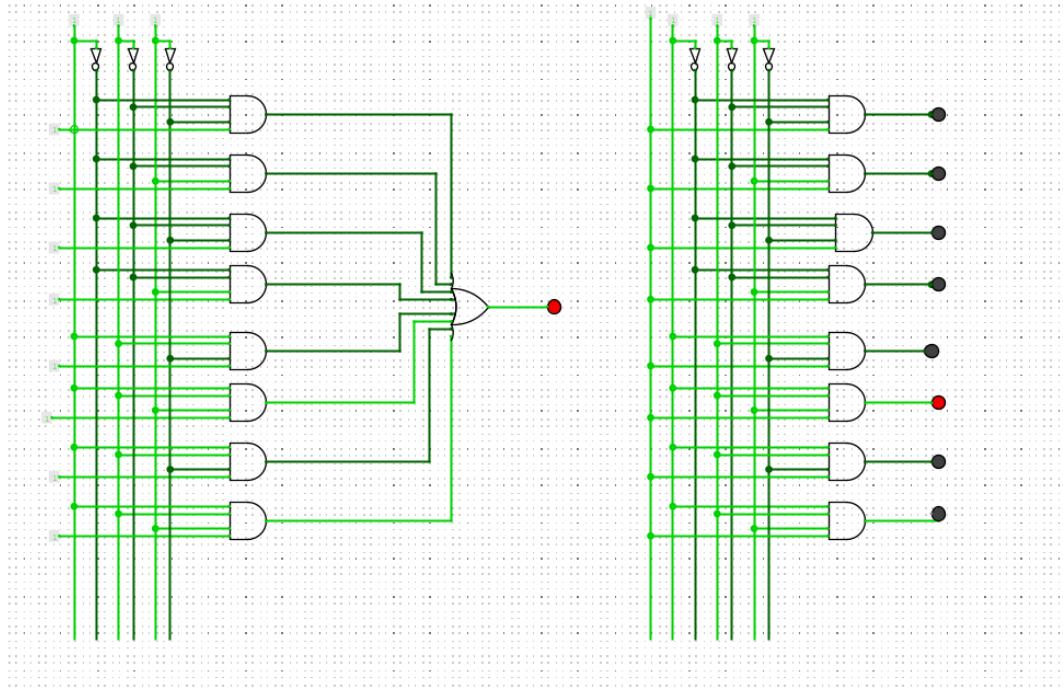

#### 2. Pembahasan Demultiplexer 1-to-8

Demultiplexer melakukan fungsi kebalikan MUX, yaitu menyalurkan satu input I ke salah satu dari delapan output ( $Y_0$ – $Y_7$ ) berdasarkan kombinasi select line ( $S_0$ ,  $S_1$ ,  $S_2$ ).

Implementasi rangkaian menggunakan gerbang AND dan NOT sesuai ekspresi logika:

$$Y_0 = S_0' \cdot S_1' \cdot S_2' \cdot I, Y_1 = S_0' \cdot S_1' \cdot S_2 \cdot I, Y_2 = S_0' \cdot S_1 \cdot S_2' \cdot I, \dots, Y_7 = S_0 \cdot S_1 \cdot S_2 \cdot I$$

Setiap output hanya bernilai 1 apabila kombinasi select line sesuai dengan pola yang ditentukan dan input I bernilai 1. Dari simulasi Logisim, LED pada output menyala sesuai perubahan select line, menunjukkan bahwa DEMUX berhasil mengarahkan sinyal input ke output yang tepat.

Melalui simulasi ini, mahasiswa dapat memahami bagaimana data tunggal dapat disalurkan ke banyak jalur hanya dengan kombinasi bit kontrol. Ini sangat relevan dalam sistem digital seperti memori, komunikasi data, dan sistem switching.

## BAB II

### KESIMPULAN

Berdasarkan praktikum yang dilakukan, dapat disimpulkan bahwa Multiplexer dan Demultiplexer merupakan rangkaian logika penting dalam sistem digital yang berfungsi untuk memilih atau menyalurkan data menggunakan sinyal kontrol. Pada MUX 8-to-1, satu output dipilih dari delapan input menggunakan tiga bit select line, sedangkan pada DEMUX 1-to-8, satu input dapat diarahkan ke salah satu dari delapan output.

Simulasi di Logisim menunjukkan bahwa kedua rangkaian bekerja sesuai tabel kebenaran dan ekspresi logika yang digunakan. Praktikum ini membantu mahasiswa memahami konsep seleksi data, perancangan rangkaian digital berbasis gerbang logika, serta cara menerapkan teori dalam bentuk rangkaian yang dapat diuji secara langsung.