# **LAPORAN PRAKTIKUM**

**Mata Kuliah**

**Pengantar Sistem Digital**

## **RANGKAIAN SEKUENSIAL – FLIP FLOP DASAR**

**Dosen: Arif R. Dwiyanto ST., MTI.**

**Disusun oleh:**

**Fenaudry Luthfiyah Gusti Dzakirah (202410715272)**

**F3A6**

**PROGRAM STUDI INFORMATIKA FAKULTAS ILMU KOMPUTER**

**UNIVERSITAS BHAYANGKARA JAKARTA RAYA**

**2025**

## BAB I

### PENDAHULUAN

#### 1.1 Tujuan Praktikum

1. Mahasiswa mampu memahami konsep rangkaian sequential.

2. Mahasiswa mampu merancang dan mensimulasikan flip-flop dasar.

3. Menganalisis pengaruh sinyal clock dan input terhadap keluaran flip-flop.

4. Memahami peran flip-flop sebagai memori satu bit dalam rangkaian digital.

#### 1.2 Langkah-langkah Praktikum

##### 1. Rangkaian SR (Set-Reset) Flip-Flop

- Membangun rangkaian SR Flip-Flop menggunakan gerbang logika NOR/NAND:

- Dua gerbang NOR/NAND dihubungkan secara umpan balik.

- Input pin S dan R dihubungkan ke masing-masing NOR/NAND.

- Hubungkan LED ke output Q dan Q'.

- Uji rangkaian dengan kombinasi input S dan R.

##### 2. Rangkaian D Filp-Flop

- Tambahkan gerbang NOT dan SR Flip-Flop:

- Hubungkan D ke S, dan D' (melalui NOT) ke R.

- Memberikan variasi logika pada input D dan clock secara bertahap.

- Simulasikan rangkaian dan verifikasi tabel kebenaran.

##### 3. Rangkaian JK Flip-Flop

- Bangun JK Flip-Flop menggunakan SR Flip-Flop dengan tambahan rangkaian pengendali.

- Menghubungkan input J dan K (00, 01, 10, 11).

- Memberikan sinyal clock secara bertahap untuk mengetahui perubahan keadaan flip-flop.

- Verifikasi tabel kebenaran.

##### 4. Rangkaian T (Toggle) Flip-Flop

- Memilih komponen flip-flop yang diperlukan dari library memory.

- Menambahkan sumber clock.

- Menhubungkan rangkaian sesuai diagram.

- Menambahkan LED pada keluaran q.

- Menjalankan simulasi dan mengaktifkan clock.

### 1.3 Hasil Simulasi

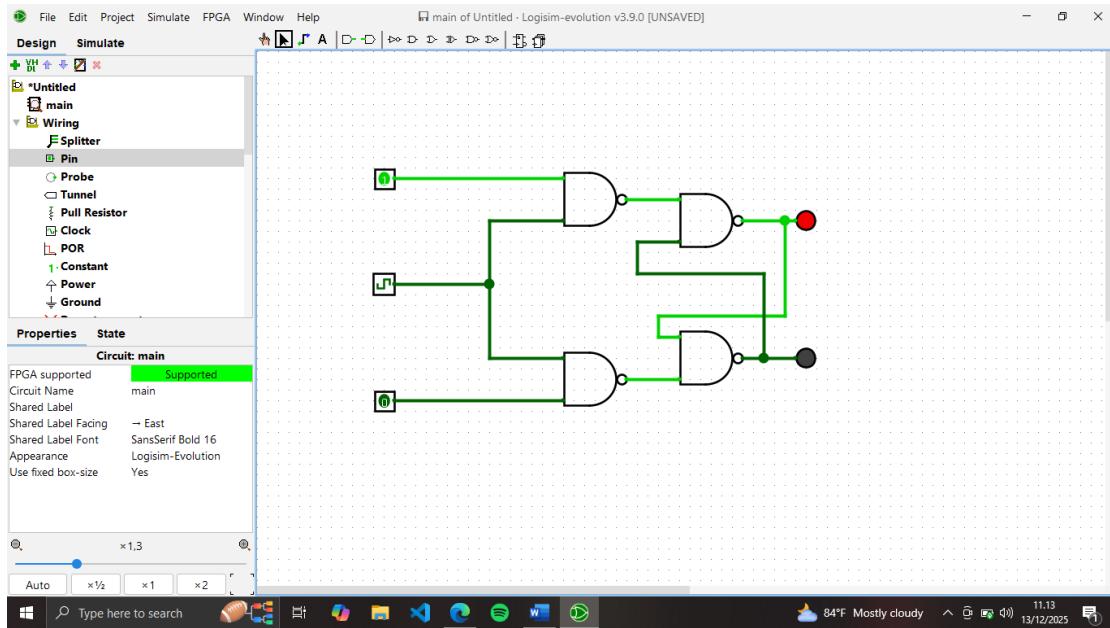

#### 1. Rangkaian SR Flip-Flop

Rangkaian hasil praktikum SR Flip-Flop berclock yang menggunakan gerbang NAND terdiri dari dua gerbang NAND di bagian kanan yang dihubungkan secara silang (cross-coupled) sehingga membentuk elemen penyimpan data dengan keluaran Q dan Q'. Sementara itu, dua gerbang NAND di bagian kiri berfungsi sebagai pengendali masukan set (S) dan reset (R) yang dikombinasikan dengan sinyal clock.

Sinyal clock diberikan ke kedua gerbang NAND pengendali, sehingga masukan S dan R hanya dapat memengaruhi latch ketika clock berada pada kondisi aktif (logika 1). Ketika clock tidak aktif, keluaran gerbang pengendali tidak mengalami perubahan, sehingga rangkaian tetap mempertahankan kondisi sebelumnya (hold). Oleh karena itu, perubahan pada masukan set atau reset tidak langsung berdampak pada keluaran selama clock tidak aktif.

Pada saat clock aktif, kombinasi nilai masukan S dan R akan menentukan keadaan keluaran. Jika S aktif, rangkaian akan berada pada kondisi set, jika R aktif maka

rangkaian berada pada kondisi reset, dan jika S serta R tidak aktif, keluaran akan tetap mempertahankan keadaan sebelumnya.

TABEL KEBENARAN

- Saat clock = 1 (aktif)

| S | R | Q(t+1) | Ket                |

|---|---|--------|--------------------|

| 0 | 0 | Q(t)   | Hold/tidak berubah |

| 0 | 1 | 0      | Reset              |

| 1 | 0 | 1      | Set                |

| 1 | 1 | x      | Kondisi terlarang  |

Saat sinyal clock bernilai 1 atau dalam keadaan aktif, SR Flip-Flop berada pada kondisi operasi. Apabila S = 0 dan R = 0, maka tidak terjadi perubahan pada keluaran sehingga flip-flop tetap mempertahankan keadaan sebelumnya (hold). Jika S = 0 dan R = 1, rangkaian akan berada pada kondisi reset sehingga keluaran Q bernilai 0. Sebaliknya, jika S = 1 dan R = 0, rangkaian berada pada kondisi set sehingga keluaran Q bernilai 1. Adapun kondisi S = 1 dan R = 1 termasuk kondisi terlarang karena dapat mengakibatkan keluaran berada pada keadaan yang tidak terdefinisi.

- Saat clock = 0 (tidak aktif)

| S | R | Q(t+1) | Ket  |

|---|---|--------|------|

| x | x | Q(t)   | Hold |

Ketika sinyal clock bernilai 0 atau dalam keadaan tidak aktif, SR Flip-Flop tidak merespons perubahan pada masukan S dan R. Berapa pun nilai S dan R, keluaran Q akan tetap mempertahankan kondisi sebelumnya. Hal ini menunjukkan bahwa sinyal clock berfungsi sebagai pengatur waktu perubahan keluaran, sehingga flip-flop hanya mengalami perubahan ketika clock berada pada kondisi aktif.

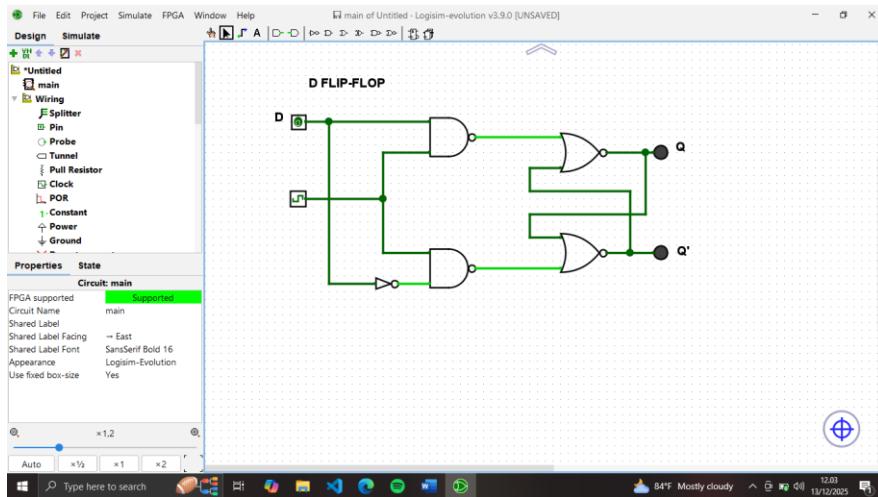

2. Rangkaian D Flip-Flop

Rangkaian hasil praktikum D Flip-Flop ber-clock disusun dari kombinasi gerbang logika berupa SR latch berbasis NOR. Rangkaian ini memiliki masukan utama berupa D (data) dan sinyal clock, dengan keluaran Q dan Q' yang saling berlawanan.

Sinyal D dibagi menjadi dua jalur, yaitu jalur langsung dan jalur yang melewati gerbang NOT (inverter) sehingga dihasilkan sinyal D dan D'. Kedua sinyal tersebut kemudian masing-masing dikombinasikan dengan sinyal clock melalui gerbang logika pada bagian kiri rangkaian. Proses ini menghasilkan sinyal set (S) dan reset (R) yang saling berlawanan, sehingga kondisi terlarang pada SR Flip-Flop dapat dihindari.

Pada bagian kanan rangkaian, dua gerbang NOR dihubungkan secara silang membentuk SR latch yang berfungsi sebagai elemen penyimpan data. Ketika sinyal clock berada pada kondisi aktif, nilai masukan D akan menentukan keadaan keluaran. Jika  $D = 1$ , rangkaian berada pada kondisi set sehingga  $Q = 1$  dan  $Q' = 0$ . Sebaliknya, jika  $D = 0$ , rangkaian berada pada kondisi reset sehingga  $Q = 0$  dan  $Q' = 1$ . Saat clock tidak aktif, sinyal set dan reset tidak mengalami perubahan, sehingga SR latch mempertahankan keadaan sebelumnya.

#### TABEL KEBENARAN

- Saat clock = 1 (aktif)

| D | $Q(t+1)$ | Ket   |

|---|----------|-------|

| 0 | 0        | Reset |

|   |   |     |

|---|---|-----|

| 1 | 1 | Set |

|---|---|-----|

Pada saat clock bernilai 1 atau aktif, D Flip-Flop akan membaca nilai input D dan langsung menyimpan ke output-mya. Jika D = 0, maka flip-flop berada pada kondisi reset sehingga output q menjadi 0. Jika D = 1, maka flip-flop berada pada kondisi set sehingga output q menjadi 1. Pada kondisi ini, nilai output selalu mengikuti input D.

- Saat clock = 0 (tidak aktif)

|   |        |                      |

|---|--------|----------------------|

| D | Q(t+1) | Ket                  |

| x | Q(t)   | Hold / tidak berubah |

Pada saat clock bernilai 0 atau tidak aktif, D Flip-Flop tidak merespons perubahan pada input D. Berapapun nilai D, output q akan tetap mempertahankan keadaan sebelumnya. Kondisi ini menunjukkan fungsi flip-flop sebagai elemen penyimpan data, di mana nilai hanya berubah ketika clock aktif dan disimpan ketika clock tidak aktif.

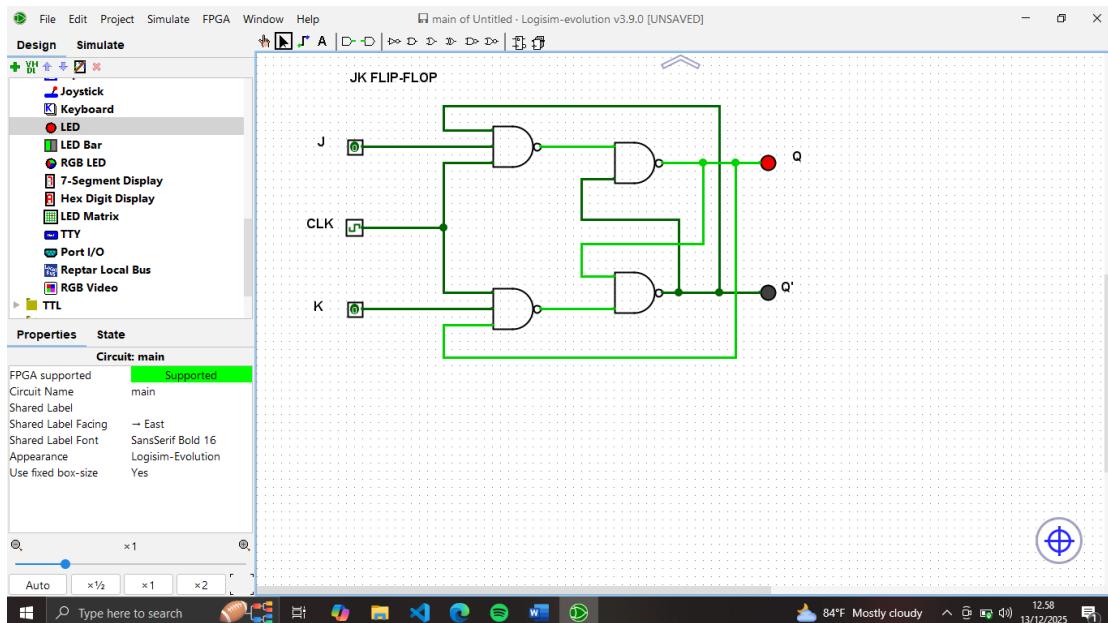

### 3. Rangkaian JK Flip-Flop

Rangkaian hasil praktikum JK Flip-Flop ber-clock disusun dari kombinasi gerbang logika dan SR latch berbasis NAND. Rangkaian ini memiliki dua masukan utama, yaitu J dan K, serta satu sinyal clock sebagai pengatur waktu, dengan keluaran Q dan Q' yang saling berlawanan.

Pada bagian kiri rangkaian, masukan J dan K masing-masing dikombinasikan dengan sinyal clock serta umpan balik dari keluaran melalui gerbang NAND. Umpan balik ini

berfungsi untuk menghilangkan kondisi terlarang yang terdapat pada SR Flip-Flop. Proses tersebut menghasilkan sinyal set dan reset yang telah dikendalikan.

Di bagian kanan rangkaian, dua gerbang NAND dihubungkan secara silang membentuk SR latch yang berfungsi sebagai penyimpan keadaan logika. Ketika sinyal clock berada dalam kondisi aktif, kombinasi nilai masukan J dan K akan menentukan keadaan keluaran. Jika  $J = 0$  dan  $K = 0$ , keluaran akan mempertahankan kondisi sebelumnya. Jika  $J = 1$  dan  $K = 0$ , flip-flop berada pada kondisi set sehingga Q bernilai 1. Sebaliknya, jika  $J = 0$  dan  $K = 1$ , flip-flop berada pada kondisi reset sehingga Q bernilai 0. Sementara itu, jika  $J = 1$  dan  $K = 1$ , keluaran akan berubah atau berpindah keadaan (toggle) setiap kali clock aktif. Saat clock tidak aktif, sinyal set dan reset tidak mengalami perubahan sehingga SR latch tetap mempertahankan keadaan sebelumnya

TABEL KEBENARAN

- Saat clock = 1 (aktif)

| J | K | $Q(t+1)$ | Ket                |

|---|---|----------|--------------------|

| 0 | 0 | $Q(t)$   | Hold /tidakberubah |

| 0 | 1 | 0        | Reset              |

| 1 | 0 | 1        | Set                |

| 1 | 1 | $Q(t)$   | Toggle             |

Pada saat clock bernilai 1 atau aktif, JK Flip-Flop merespons kombinasi input J dan K. Jika  $J = 0$  dan  $K = 0$ , output akan mempertahankan keadaan sebelumnya. Jika  $J = 1$  dan  $K = 0$ , flip-flop berada pada kondisi set sehingga  $q = 1$ . Jika  $J = 0$  dan  $K = 1$ , flip-flop berada pada kondisi reset sehingga  $q = 0$ . Sedangkan jika  $J = 1$  dan  $K = 1$ , output akan berpindah keadaan (toggle) pada setiap clock.

- Saat clock = 0 (tidak aktif)

| J | K | $Q(t+1)$ | Ket  |

|---|---|----------|------|

| x | x | $Q(t)$   | Hold |

Pada saat clock bernilai 0 atau tidak aktif, perubahan nilai J dan k tidak memengaruhi output. Flip-Flop akan tetap menyimpan keadaan terakhirnya yang menunjukkan fungsi clock sebagai pengendali perubahan output pada rangkaian sequential.

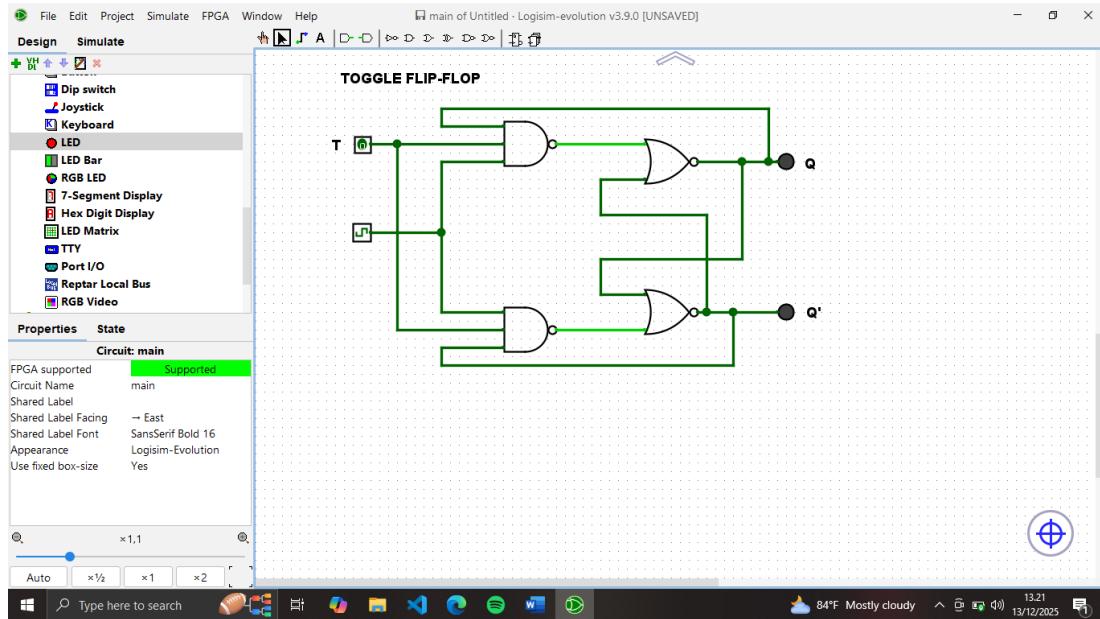

#### 4. Rangkaian T (Toggle)

Rangkaian hasil praktikum Toggle Flip-Flop ber-clock disusun dari kombinasi gerbang logika serta SR latch berbasis NAND dan NOR. Rangkaian ini memiliki satu masukan utama, yaitu T, dan satu sinyal clock sebagai pengatur waktu, dengan keluaran Q dan Q' yang saling berlawanan.

Pada bagian kiri rangkaian, masukan T dikombinasikan dengan sinyal clock melalui gerbang NAND sehingga menghasilkan sinyal kendali yang menuju bagian penyimpanan. Proses ini berfungsi untuk menentukan waktu perubahan keadaan flip-flop, yaitu hanya ketika sinyal clock berada pada kondisi aktif.

Pada bagian kanan rangkaian, dua gerbang NOR dihubungkan secara silang membentuk SR latch yang berperan sebagai elemen penyimpan keadaan logika. Saat clock aktif dan  $T = 1$ , keluaran Q akan berubah ke kondisi kebalikan dari keadaan sebelumnya (toggle). Jika sebelumnya Q bernilai 0 maka akan menjadi 1, dan sebaliknya. Namun, apabila  $T = 0$ , keluaran akan tetap mempertahankan keadaan sebelumnya. Ketika clock tidak aktif, sinyal kendali tidak memengaruhi SR latch sehingga rangkaian tetap menyimpan nilai terakhirnya.

TABEL KEBENARAN

- Saat clock = 1 (aktif)

| T | Q(t) | Q(t+1) | Ket                |

|---|------|--------|--------------------|

| 0 | 0    | 0      | Hold/tidak berubah |

| 0 | 1    | 1      | Hold/tidak berubah |

| 1 | 0    | 1      | Toggle/ubah ke 1   |

| 1 | 1    | 0      | Toggle/ubah ke 0   |

Pada saat clock bernilai 1 atau aktif, T Flip-Flop merespons input T. Jika T = 0, output mempertahankan keadaan sebelumnya (hold). Jika T = 1, output berbalik dari keadaan sebelumnya (toggle). Flip-flop hanya berubah saat ada pulsa clock aktif.

- Saat clock = 0 (tidak aktif)

| T | Q(t) | Q(t+1) | Ket  |

|---|------|--------|------|

| X | 0    | 0      | Hold |

| X | 1    | 1      | Hold |

Saat clock bernilai 0 atau tidak aktif, perubahan input T tidak memengaruhi output.

Flip-flop tetap menyimpan keadaan terakhir, menunjukkan fungsi clock sebagai pengendali perubahan output pada rangkaian sequential.

#### 1.4 Kesimpulan

Berdasarkan hasil praktikum flip-flop, dapat disimpulkan bahwa flip-flop merupakan rangkaian sekuensial yang keluarannya dipengaruhi oleh nilai masukan serta keadaan sebelumnya. Pada SR Flip-Flop, masukan S dan R menentukan kondisi set, reset, atau hold. Pada D Flip-Flop, masukan D secara langsung menentukan nilai keluaran Q ketika sinyal clock aktif. Pada JK Flip-Flop, kombinasi masukan J dan K menentukan kondisi set, reset, hold, maupun toggle. Sementara itu, pada T Flip-Flop, masukan T menentukan apakah keluaran akan mempertahankan keadaan sebelumnya (hold) atau berubah ke keadaan kebalikan (toggle). Perubahan keluaran pada seluruh jenis flip-flop hanya terjadi saat sinyal clock berada pada kondisi aktif, sehingga clock berfungsi sebagai pengendali waktu perubahan keluaran pada rangkaian sekuensial.